### TAUFIK ABRÃO

Engenheiro Eletricista, Escola Politécnica da USP, 1992

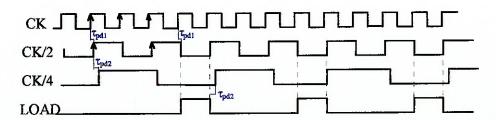

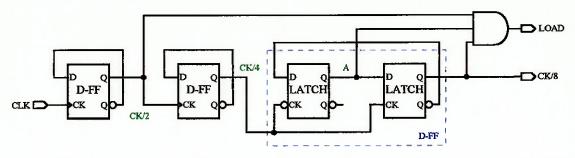

# CIRCUITOS INTEGRADOS DIGITAIS DE ALTA VELOCIDADE EM GaAs: DEMULTIPLEXADOR DE 16 CANAIS EM 2,5 Gb/s

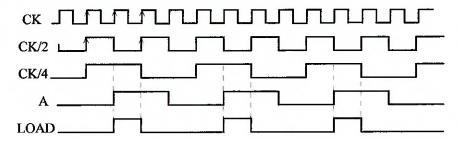

Dissertação apresentada à Escola Politécnica da Universidade de São Paulo como parte dos requisitos necessários à obtenção do título de Mestre em Engenharia Elétrica.

Orientadora: Dra. FÁTIMA SALETE CORRERA

## TAUFIK ABRÃO

Engenheiro Eletricista, Escola Politécnica da USP, 1992

# CIRCUITOS INTEGRADOS DIGITAIS DE ALTA VELOCIDADE EM GaAs: DEMULTIPLEXADOR DE 16 CANAIS EM 2,5 Gb/s

Dissertação apresentada à Escola Politécnica da Universidade de São Paulo como parte dos requisitos necessários à obtenção do título de Mestre em Engenharia Elétrica.

Área de Concentração:

MICROELETRÔNICA

Orientadora:

Dra. FÁTIMA SALETE CORRERA

São Paulo 1996

# UNIVERSIDADE DE SÃO PAULO ESCOLA POLITÉCNICA

# TERMO DE JULGAMENTO DE DEFESA DE DISSERTAÇÃO DE MESTRADO

| Aos 21 dias do mês de maio de 1996, às 10:00 horas, no Departamento de Engenharia Eletrônica da Escola Politécnica da Universidade de São Paulo, presente a Comissão Julgadora, integrada pelos Senhores |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Professores Doutores Fátima Salete Correra, orientadora do candidato. José Vieira do Vale Neto e Ricardo Guerra Pereira iniciou-se a Defesa de                                                           |

| Dissertação de Mestrado do Senhor TAUFIK ABRÃO.                                                                                                                                                          |

| Título da Dissertação: "CIRCUITOS INTEGRADOS DIGITAIS DE ALTA VELOCIDADE EM GAAS: DEMULTIPLEXADOR DE 16 CANAIS EM 2,5 Gb/s".                                                                             |

| Concluída a argüição, procedeu-se ao julgamento na forma regulamentar, tendo a Comissão Julgadora Atribuído ao candidato as                                                                              |

| seguintes notas: Profa.Dra. Fátima Salete Correra(10)(de-2)                                                                                                                                              |

| Prof. Dr. José Vieira do Vale Neto                                                                                                                                                                       |

| Para constar, é lavrado o presente termo, que vai assinado pela Comissão Julgadora e pela Secretária de Pós-Graduação.                                                                                   |

|                                                                                                                                                                                                          |

| São Paulo, 21 de maio de 1996.                                                                                                                                                                           |

| Presidente: Toterna Jakit Korna<br>Kando Guna Lewing Jon on And. J                                                                                                                                       |

|                                                                                                                                                                                                          |

| Secretária Mara Fátima de Jesus Luz Sanches wantes                                                                                                                                                       |

| Observações: Apacido "COALLOLEVO?"                                                                                                                                                                       |

| Homologado pela C.P.G. em reunião realizada à 1f / 06 / 1996.                                                                                                                                            |

| Tomoro pour cirio. Citi routino routizana a                                                                                                                                                              |

PEE

Universidade de São Paulo Biblioteca da Escola Politégnica

À minha família e À Maria Josefa,

com carinho.

Este trabalho foi realizado com o apoio financeiro das seguintes entidades:

- Laboratório de Microeletrônica da USP LME USP

- CPqD-Telebrás, contratos Telebrás-USP JDPqD-516/93 e JDPqD-586/94

#### **AGRADECIMENTOS**

(

À minha orientadora Dra. Fátima Salete Correra, pela orientação, dedicação e amizade, que muito contribuíram para a minha formação;

Ao Dr. Edmar Camargo, pela iniciação às atividades acadêmicas na área de microondas;

Ao Dr. José Kleber da Cunha Pinto, coordenador geral do Laboratório de Microeletrônica;

A todos os colegas do Laboratório de Microeletrônica da USP, pela compreensão, pelo respeito e incentivo durante a realização deste trabalho.

Aos colegas do CPqD/TELEBRÁS, pela realização do leiaute do circuito projetado e pela contribuição na caracterização do CI.

Ao Dr. Wilhelmus Van Noije do Laboratório de Sistemas Integráveis da USP, LSI, pelo empréstimo de equipamentos por ocasião da caracterização final do CI.

A todos aqueles que de uma forma ou de outra colaboraram para a realização deste trabalho.

# **SUMÁRIO**

| LISTA DE SIGLAS                                                        |          |

|------------------------------------------------------------------------|----------|

| LISTA DE SÍMBOLOS                                                      |          |

| RESUMO                                                                 |          |

| "ABSTRACT"                                                             |          |

| 1. INTRODUÇÃO                                                          |          |

| 1.1 BREVE HISTÓRICO E APLICAÇÕES DE CI'S EM GaAS                       | 1        |

| 1.2 OBJETIVOS DA DISSERTAÇÃO                                           | 3        |

| 1.2.1 Capacitação em projetos de alta velocidade                       | 4        |

| 1.2.2 Uso de Foundry Externa                                           | 6        |

| 1.3 DESCRIÇÃO DO CONTEÚDO DOS CAPÍTULOS                                | 7        |

| 2. TECNOLOGIAS DE CI'S DIGITAIS DE ALTA VELOCIDADE                     |          |

| 2.1 INTRODUÇÃO                                                         | 8        |

| 2.2 COMPARAÇÃO COM OUTRAS TECNOLOGIAS                                  | 8        |

| 2.3 FAMÍLIAS LÓGICAS QUE EMPREGAM MESFET EM GaAs                       | 13       |

| 2.3.1 Portas lógicas Normalmente-ON                                    | 17       |

| 2.3.2 Portas lógicas Normalmente-OFF                                   | 20       |

| 2.3.3 Desempenho em termos do produto velocidade - consumo de potência | 32       |

| 2.4 FOUNDRIES DE CI'S DIGITAIS DE ALTA VELOCIDADE EM GaAS              |          |

| COM SERVIÇOS MULTI-USUÁRIOS                                            |          |

| 2.4.1 Critérios de seleção de foundry                                  |          |

| 2.4.2 Foundries selecionadas                                           | 39<br>44 |

| 2.4.5 Conclusões da ananse comparativa dos serviços de foundry         | 44       |

| 3. DEMULTIPLEXADOR DE ALTA VELOCIDADE: TOPOLOGIAS                      |          |

| 3.1 INTRODUÇÃO                                                         | 46       |

| 3.2 CRITÉRIOS PARA A SELEÇÃO DA TOPOLOGIA DO DEMUX                     | 46       |

| 3.2.1 Funcionalidade                                                   | 47  |

|------------------------------------------------------------------------|-----|

| 3.2.2 Compactação: número de elementos ativos necessários              | 48  |

| 3.2.3 Realização da topologia em termos de células padrão              | 49  |

| 3.3 TOPOLOGIAS DE DEMULTIPLEXADOR ANALISADAS                           | 49  |

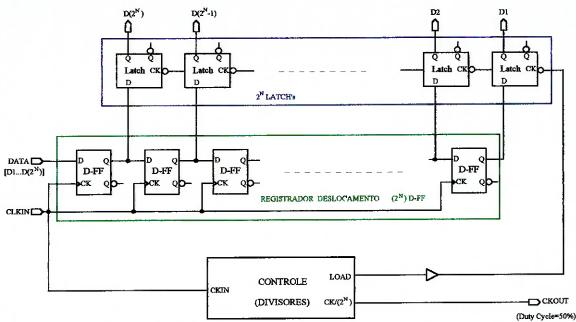

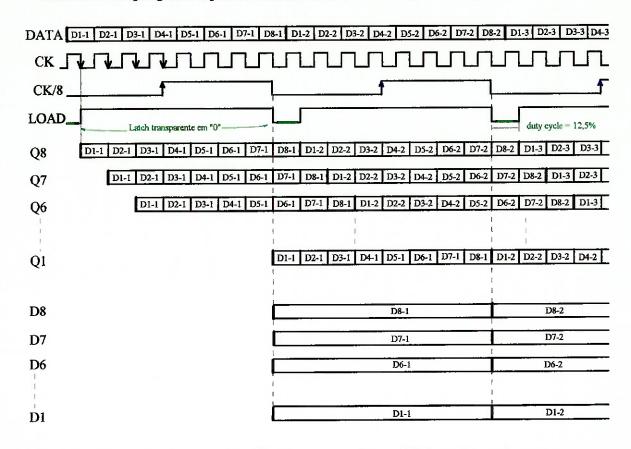

| 3.3.1 Registrador de Deslocamento Clássico                             | 49  |

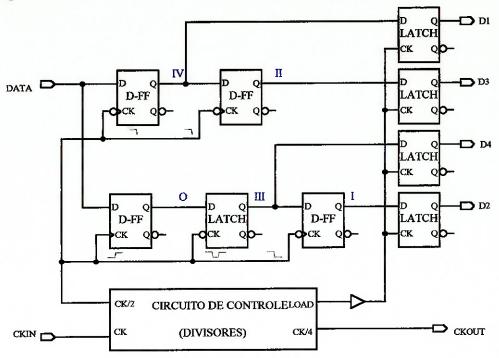

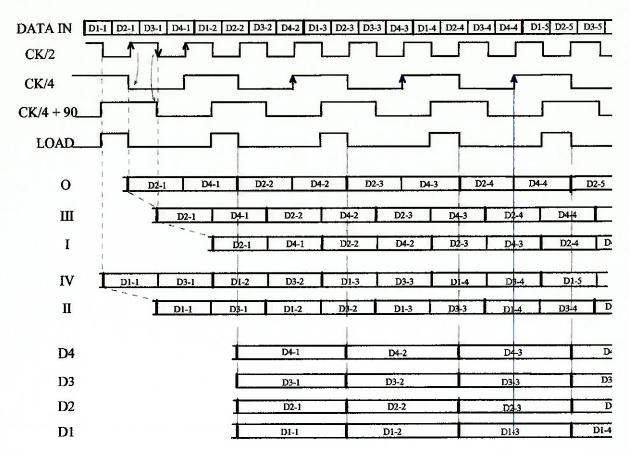

| 3.3.2 Registrador de Deslocamento Modificado I                         | 52  |

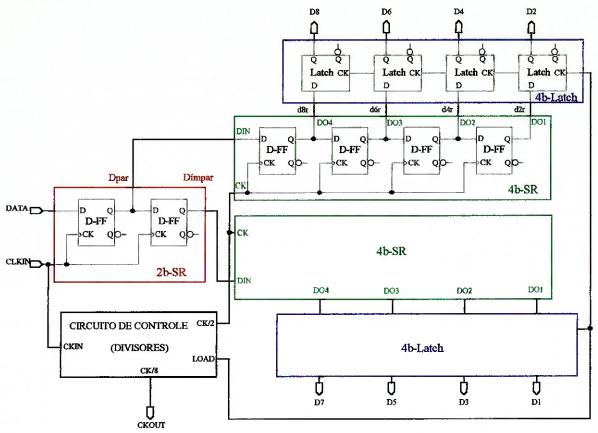

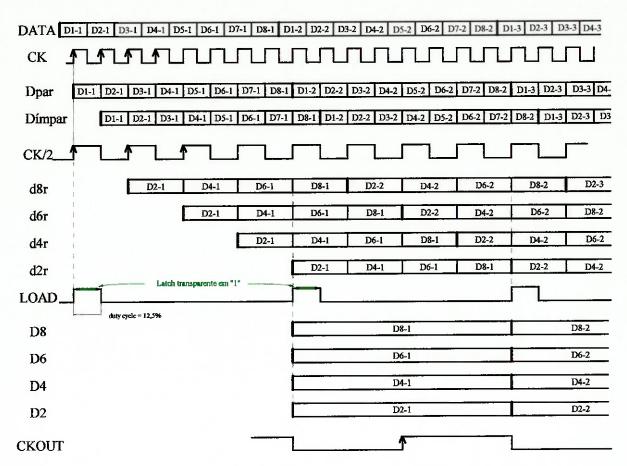

| 3.3.3 Registrador de Deslocamento Modificado II                        | 54  |

| 3.3.4 Circuito de Controle (Divisores)                                 | 56  |

| 3.3.4.a Contador Síncrono (ou Anel)                                    | 56  |

| 3.3.4.b Contador "Ripple" (ou Assíncrono)                              | 59  |

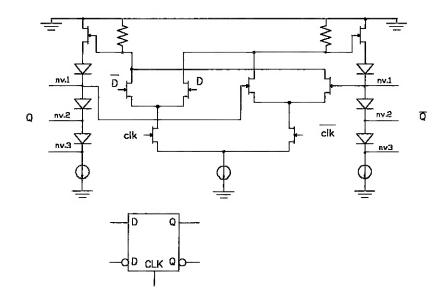

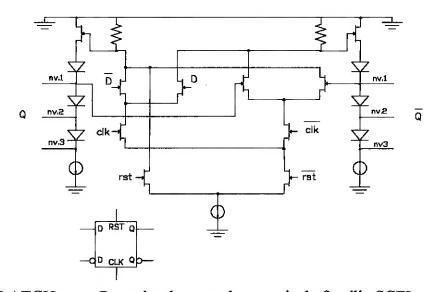

| 3.3.5 Árvore com flip-flop tipo D                                      | 61  |

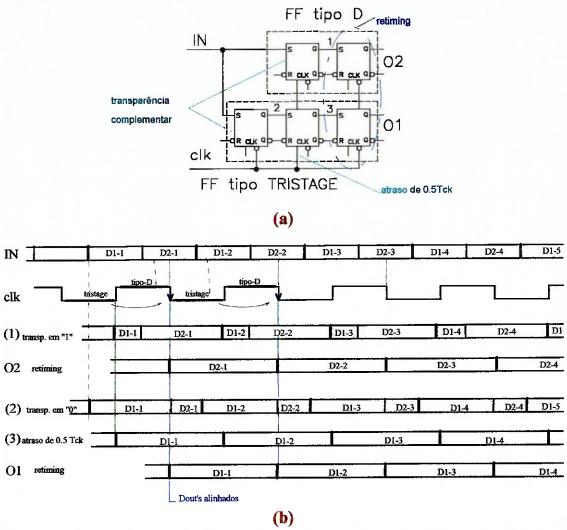

| 3.3.6 Árvore com flip-flop tipo D e Tristage                           | 64  |

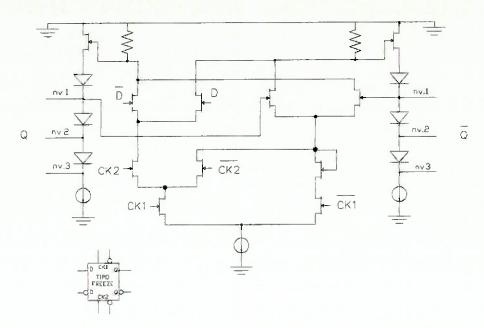

| 3.3.7 Árvore com flip-flop tipo Tristage e latch tipo Freeze           | 68  |

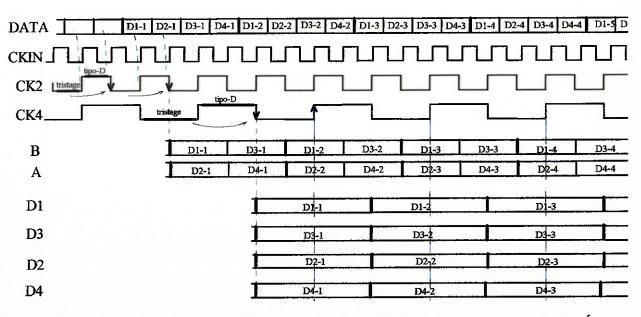

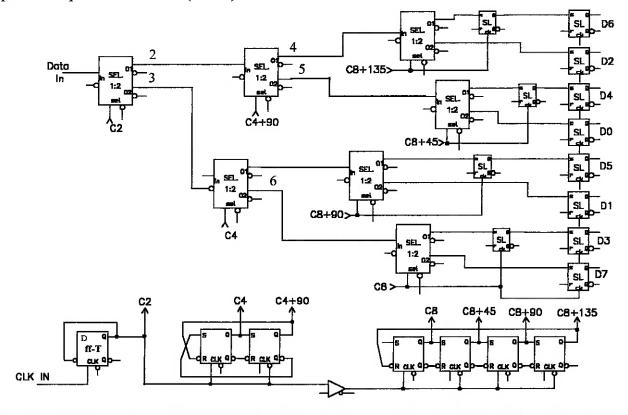

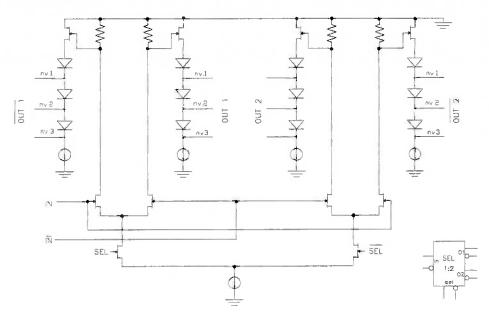

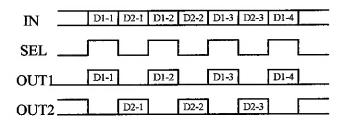

| 3.3.8 Árvore com seletores 1:2                                         | 72  |

| 3.3.9 Paralela                                                         | 76  |

| 3.3.9.a Paralela com flip-flop tipo D                                  | 77  |

| 3.3.9.b Paralela com flip-flop tipo D/Tristage                         | 79  |

| 3.3.10 Árvore-Paralela com flip-flop tipo D/Tristage                   | 81  |

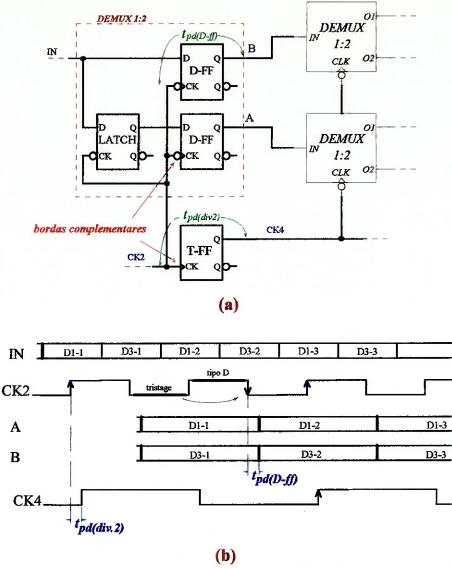

| 3.3.11 Primeiro Divisor por 2: implementações alternativas             | 84  |

| 3.3.11.a Divisor por 2 Regenerativo                                    | 84  |

| 3.3.11.b Divisor por 2 Dinâmico                                        | 86  |

| 3.3.12 Comparação entre Topologia Árvore e Registrador de Deslocamento | 89  |

| 3.4 TOPOLOGIAS DE CIRCUITO DE SKIP ANALISADAS                          | 94  |

| 3.4.1 Skip Série empregando seletor 2:1ou XOR                          | 95  |

| 3.4.2 Skip Série empregando registrador de deslocamento                | 97  |

| 3.4.3 Skip Série empregando contador módulo 3                          | 98  |

| 3.4.4 Skip Paralelo com seletores 2:1 e remultiplexagem                | 99  |

| 3.4.5 Skip Paralelo empregando XOR nos ramos dos sinais de relógio     | 101 |

| 3.4.6 Comparação entre circuitos de Skip analisados                    | 105 |

| 3.5 CONCLUSÕES                                                         | 106 |

|                                                                        |     |

| 4. PROJETO DO DEMULTIPLEXADOR                                          |     |

|                                                                        |     |

| 4.1 INTRODUÇÃO                                                         | 107 |

| 4.2 ESPECIFICAÇÕES DO CI                                               | 108 |

| 4.3 SELEÇÃO DA FOUNDRY E CONSEQUENTES RESTRIÇÕES                       | 109 |

| 4.3.1 Características da foundry TriQuint Semiconductor                | 109 |

| 4 3 2 Limitações da taya de operação das células padrão da TriQuint    | 111 |

| 4.3.3 Limitações do projeto devido ao uso da foundry TriQuint               | 113 |

|-----------------------------------------------------------------------------|-----|

| 4.3.4 Sub-Blocos integrantes do demultiplexador especificado                | 113 |

| 4.3.5 Características globais de entrada e saída do demultiplexador         | 115 |

| 4.4 TOPOLOGIA DE DEMULTIPLEXADOR E DE SKIP ESCOLHIDAS                       | 118 |

| 4.5 CONSIDERAÇÕES DE PROJETO EM TAXAS DE Gb/s                               |     |

| EMPREGANDO CÉLULAS PADRÃO QLSI-TriQuint                                     | 120 |

| 4.5.1 Considerações Gerais                                                  | 120 |

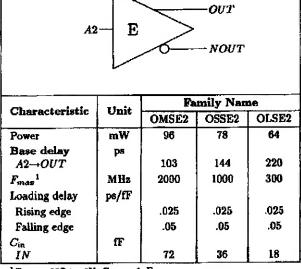

| 4.5.2 Parâmetros Potência-Velocidade e Carregamento Capacitivo              | 127 |

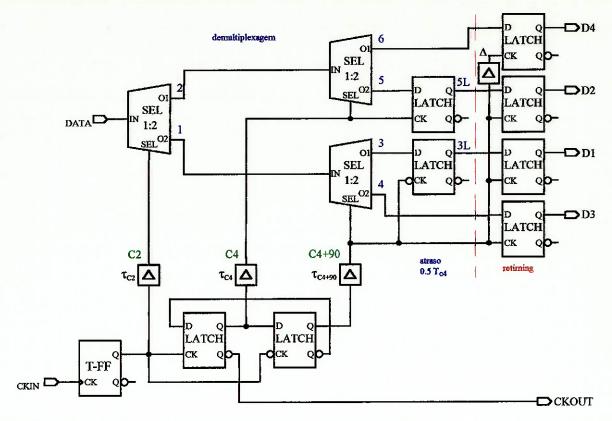

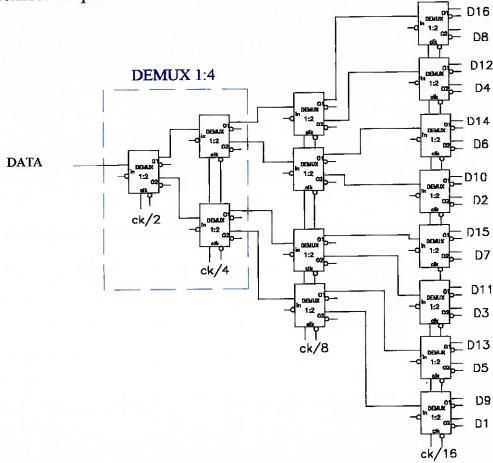

| 4.5.3 Projeto do Demultiplexador 1:4 e 1:16                                 | 132 |

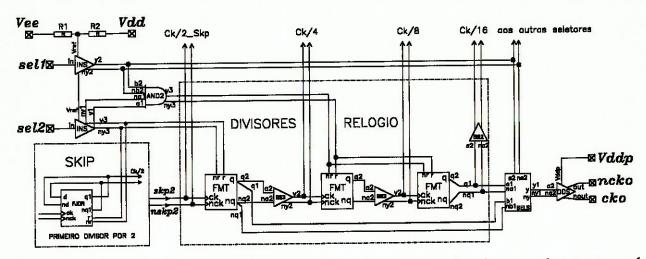

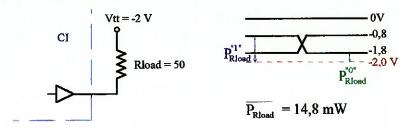

| 4.5.4 Projeto dos Divisores de Relógio                                      | 134 |

| 4.5.5 Projeto do Circuito de Seleção de Modo Demux 1:4/1:16                 |     |

| e do Circuito Desabilitador das Saídas                                      | 136 |

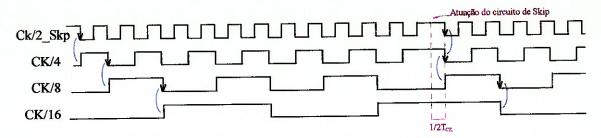

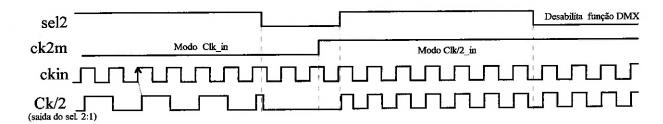

| 4.5.6 Projeto do Circuito de Skip Série empregando Seletores 2:1 Modificado | 139 |

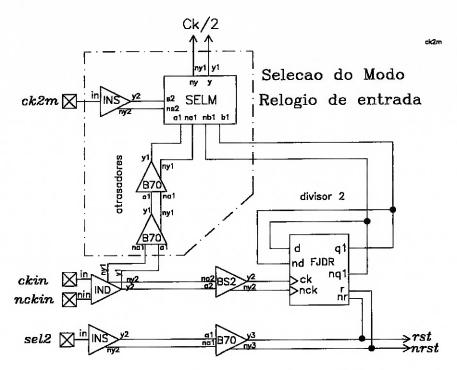

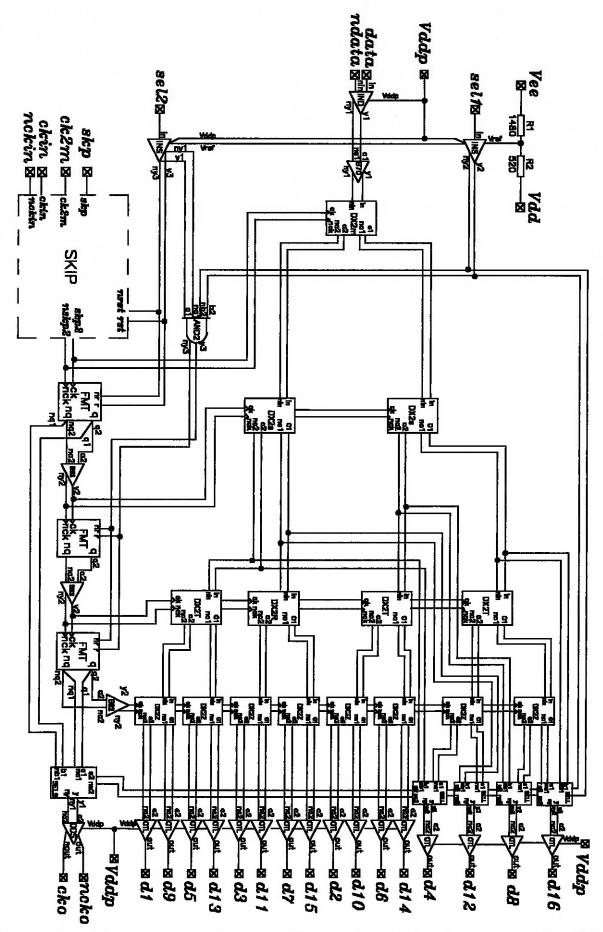

| 4.5.7 Projeto do Circuito Habilitador do Modo de Relógio CK/2               | 142 |

| 4.5.8 Avaliação da Área necessária                                          | 146 |

| 4.6 SIMULAÇÕES LÓGICAS                                                      | 150 |

| 4.6.1 Vetores de Testes Longos                                              | 151 |

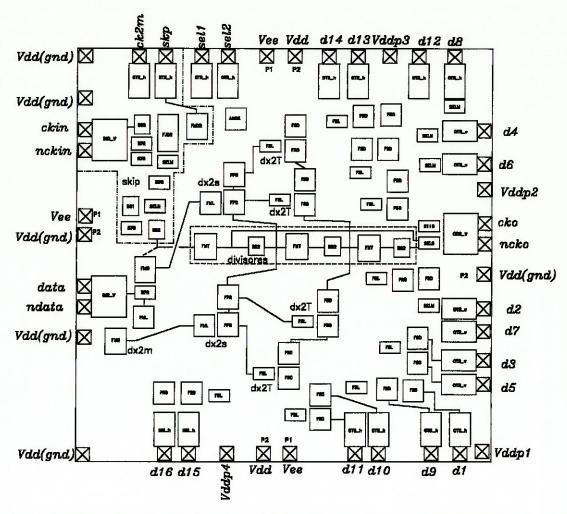

| 4.7 CONSIDERAÇÕES DE LEIAUTE                                                | 156 |

| 4.7.1 Procedimento geral de leiaute                                         | 157 |

| 4.7.2 Considerações sobre o "floorplanning" utilizado                       | 160 |

| 4.7.3 Roteamento                                                            | 160 |

| 4.7.4 Resultados da extração de parasitas - "back-annotation"               | 161 |

| 4.7.5 Pontos críticos no desenvolvimento do leiaute                         | 162 |

|                                                                             |     |

| 5. RESULTADOS EXPERIMENTAIS DO DEMULTIPLEXADOR                              |     |

| 5.1 INTRODUÇÃO                                                              | 164 |

| 5.2 CARACTERIZAÇÃO DE DEMULTIPLEXADORES DE                                  |     |

| ALTA VELOCIDADE                                                             | 164 |

| 5.3 MEDIDAS                                                                 | 166 |

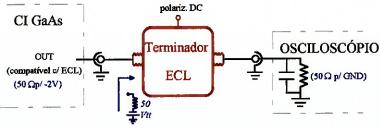

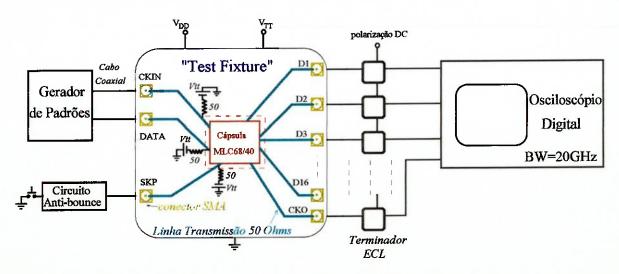

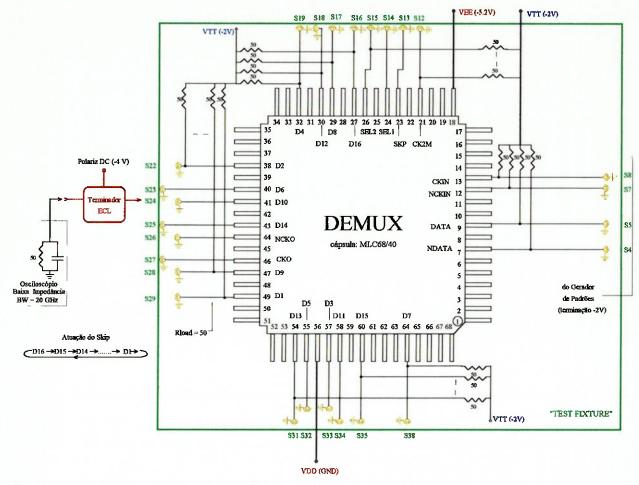

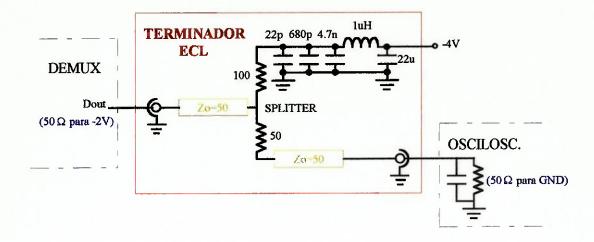

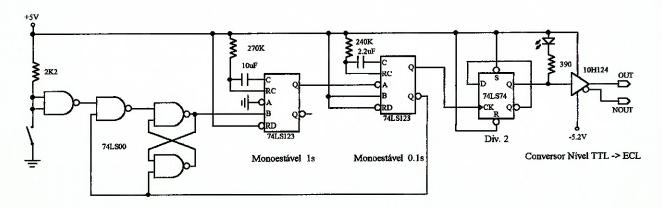

| 5.3.1 Setup de Medidas                                                      | 167 |

| 5.3.2 Parâmetros Medidos e Resultados                                       | 170 |

| 5.4 COMPARAÇÃO DOS RESULTADOS COM OS DA LITERATURA                          | 182 |

| 5 5 CONCLUSÕES                                                              | 195 |

(

(

(

0000

| 6. CONCLUSÕES E SUGESTÕES PARA TRABALHOS FUTUROS |     |

|--------------------------------------------------|-----|

| 6.1 CONCLUSÕES GERAIS                            | 186 |

| 6.2 SUGESTÕES PARA TRABALHOS FUTUROS             | 187 |

| 7. APÊNDICES                                     |     |

| APÊNDICE A4.1.a                                  | 188 |

| APÊNDICE A4.1.b                                  | 188 |

| APÊNDICE A4.2                                    | 189 |

| APÊNDICE A4.3                                    | 195 |

| APÊNDICE A5.1                                    | 203 |

| APÊNDICE A5.2                                    | 203 |

|                                                  |     |

| 8. REFERÊNCIAS BIBLIOGRÁFICAS                    |     |

#### LISTA DE SIGLAS

BDCFL ..... Buffered DCFL

BER ...... Taxa de Erro de Bit

BFL ..... Buffer FET Logic

BW ...... Faixa de frequência de passagem

B-ISDN ...... Broadband Integrated Services Digital Networks

CAE ...... Computer Aided Enginnering

CCFL ...... Capacitor-Coupled FET Logic

CDFL ...... Capacitor-Diode FET Logic

CMOS ...... Complementar MOS

CMRR ...... Relação de rejeição em modo comum de amplificação

(em amplificadores diferenciais)

DCFL ...... Direct Coupled FET Logic

D-FET ..... FET de modo depleção,  $V_{th} < 0V$

E-FET ..... FET de modo enriquecimento,  $V_{th} > 0V$

GaAs ...... Arseneto de Gálio

Gb/s ..... Gigabits por segundo

HBT ...... Heterojunction Bipolar Transistor

HEMT ...... High Electron Mobility Transistor

LBFL ..... Low Power BFL

LSCFL ..... Low Power Source Coupled FET Logic

LSI ...... Circuito integrado com escala de integração alta

MESFET ...... Metal-Semiconductor Field Efect Transistor

MMIC ...... Monolitic Microwave Integrated Circuit

MOS ...... Metal Oxid Semiconductor

MSI ...... Circuito integrado com escala de integração média

NMOS ..... MOS canal n

PCM ...... "Process Control Monitor": estruturas padrão para o

monitoramento dos parâmetros de processo durante as

etapas de construção de CI's.

QFL ...... Quasi-FET Logic

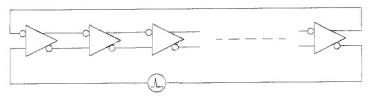

RO ...... Oscilador em anel

SCFL ..... Source Coupled FET Logic

| SDFL  | Schottky Diode FET Logic                                                                                   |

|-------|------------------------------------------------------------------------------------------------------------|

| SDH   | Synchronous Digital Hierarchy                                                                              |

| SONET | Synchronous Optical Network                                                                                |

| OC-12 | Sistema de comunicação de padrão SONET com taxa de 622 Mb/s, equivalente ao sistema de padrão SDH STM-4    |

| OC-48 | Sistema de comunicação de padrão SONET com taxa de 2,488 Gb/s, equivalente ao sistema de padrão SDH STM-16 |

| VLSI  | Circuito integrado com escala de integração muito alta                                                     |

(

# LISTA DE SÍMBOLOS

| C <sub>fan-out</sub>      | Somatória das capacitâncias de entrada, C <sub>in</sub> , de todas a células conectadas à saída da célula analisada. |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| C <sub>gd</sub>           | Capacitância porta-dreno de um tansistor MESFET                                                                      |  |  |

| C <sub>in</sub>           | Capacitância de entrada característica da porta lógica                                                               |  |  |

| C <sub>load</sub>         | Capacitância total de carga na saída da célula                                                                       |  |  |

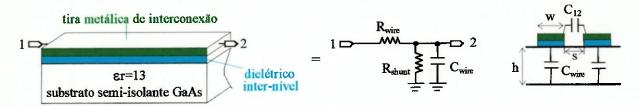

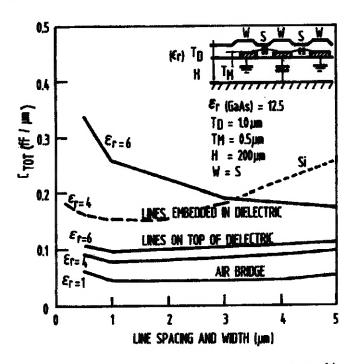

| C <sub>12</sub>           | Capacitância de crosstalk, ou entre linhas de interconexão adjacentes, separadas por uma distância s                 |  |  |

| Cwire                     | Capacitância parasitária das trilhas de interconexão entre<br>células                                                |  |  |

| DC                        | Ciclo de trabalho de um sinal periódico                                                                              |  |  |

| Demux 1:2 <sup>N</sup>    | Demultiplexador de ordem N                                                                                           |  |  |

| FI                        | Fan-in de uma porta lógica                                                                                           |  |  |

| FO                        | Fan-out de uma porta lógica                                                                                          |  |  |

| $f_{osc}$                 | Frequência de oscilação de um oscilador em anel                                                                      |  |  |

| $\mathbf{f}_{\mathrm{T}}$ | Frequência de operação na qual o ganho de corrente do transistor é unitário                                          |  |  |

| $f_{toggle}$              | Frequência máxima de operação de um elemento de memória configurado como divisor por dois.                           |  |  |

| Н                         | Espessura do substrato semicondutor                                                                                  |  |  |

| J <sub>s</sub>            | Densidade de corrente reversa do diodo                                                                               |  |  |

| K                         | Taxa de ocupação da tensão de dreno durante o tempo de transição de nível lógico "1" → "0"                           |  |  |

| 1                         | Comprimento físico da conexão metálica entre células                                                                 |  |  |

| L <sub>g</sub>            | Comprimento de canal do MESFET                                                                                       |  |  |

| Loading Delay             | Fator de sensibilidade ao carregamento de saída de uma célula                                                        |  |  |

| Load Delay <sub>max</sub> | Atraso de carregamento máximo permitido em uma célula devido ao carregamento capacitivo de saída                     |  |  |

| m                         | Número ímpar de inversores em um oscilador em anel                                                                   |  |  |

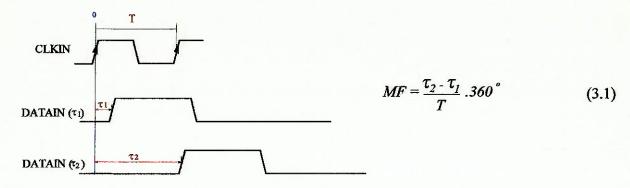

| M.F                       | Margem de Fase                                                                                                       |  |  |

| n                         | Fator de idealidade do diodo                                                                                         |  |  |

| N                         | Ordem de multiplexagem e/ou demultiplexagem                                                                          |  |  |

| NI                        | Imunidade a ruído                                                                                                    |  |  |

| NM                                                                                                                         | Margem de Ruído de uma porta lógica                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NM <sup>0</sup>                                                                                                            | Margem de Ruído para o nível lógico de entrada "0"                                                                                                                           |

| NM <sup>1</sup>                                                                                                            | Margem de Ruído para o nível lógico de entrada "1"                                                                                                                           |

| P <sub>diss</sub>                                                                                                          | Potência consumida por uma porta lógica                                                                                                                                      |

| R <sub>on</sub>                                                                                                            | resistência de saída do transistor em condução                                                                                                                               |

| R <sub>sheet</sub>                                                                                                         | Resistência de folha de um metal de interconexão                                                                                                                             |

| R <sub>wire</sub>                                                                                                          | Resistência série das trilhas de interconexão entre células                                                                                                                  |

| s                                                                                                                          | Espaçamento entre duas interconexões metálicas adjacentes                                                                                                                    |

| T                                                                                                                          | Período do sinal de relógio ou duração do sinal de dados em um demultiplexador                                                                                               |

| t <sub>f</sub>                                                                                                             | Tempo para o sinal lógico na saída de uma porta lógica excursionar de "1" até "0", medido entre 10 e 90% ou 20 e 80% das tensões nominais correspondentes ao níveis lógicos. |

| t <sub>hold</sub>                                                                                                          | Tempo de manutenção do dado em um flip-flop                                                                                                                                  |

| t <sub>pw</sub>                                                                                                            | Largura de pulso mínima em uma porta lógica ou elemento de memória.                                                                                                          |

| t <sub>r</sub>                                                                                                             | Tempo para o sinal lógico na saída de uma porta lógica excursionar de "0" até "1", medido entre 10 e 90% ou 20 e 80% das tensões nominais correspondentes ao níveis lógicos. |

| t <sub>setup</sub>                                                                                                         | Tempo de preparação do dado em um flip-flop                                                                                                                                  |

| <i>t</i> <sub>0-90%</sub>                                                                                                  | Tempo necessário para que a tensão de saída em uma rede RC varie de 0 a 90% de seu valor final                                                                               |

| T <sub>CK</sub>                                                                                                            | Período do sinal de relógio                                                                                                                                                  |

| T <sub>CK/2</sub> <sup>N</sup>                                                                                             | Período do sinal de relógio dividido por 2 <sup>N</sup>                                                                                                                      |

| u.a                                                                                                                        | Unidade de área relativa de células-padrão                                                                                                                                   |

| $V_{bi}\;$                                                                                                                 | Potencial de junção do diodo porta-fonte                                                                                                                                     |

| $V_{\text{ds}} \dots \dots \dots$                                                                                          | Tensão dreno-fonte do tansistor MESFET                                                                                                                                       |

| $V_{\text{high}} \dots \dots$                                                                                              | Tensão, em volts, correspondente ao nível lógico "1"                                                                                                                         |

| $V_{low} \dots \dots$                                                                                                      | Tensão, em volts, correspondente ao nível lógico "0"                                                                                                                         |

| $V_{\mathtt{p}} \ldots \ldots \ldots$                                                                                      | Tensão de pinch-off do transistor: tensão através do canal totalmente depletado                                                                                              |

| $V_{sw} \dots \dots$ | Excursão lógica, em volts, entre os níveis "0" e "1"                                                                                                                         |

|                                                                                                                            |                                                                                                                                                                              |

(

| $V_{th} \dots \dots$ | Tensão de porta-fonte de limiar acima da qual ocorre a condução do transistor                                |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| w                                                                                                                          | Largura física da conexão metálica entre células                                                             |

| $W_g \ldots \ldots \ldots$                                                                                                 | Largura de canal do MESFET                                                                                   |

| α <sub>nom</sub>                                                                                                           | Fase relativa nominal entre o sinal de dados e de relógio, na entrada ou saída em um demultiplexador.        |

| α‰                                                                                                                         | Desvio percentual em relação à fase relativa nominal                                                         |

| ε <sub>r</sub>                                                                                                             | Constante dielétrica relativa do material                                                                    |

| $\theta_{ck2,dat} \dots \dots \dots$                                                                                       | Fase relativa entre sinal de relógio e dados na entrada do primeiro bloco Demux 1:2, em uma topologia árvore |

| $\tau_{pd}$                                                                                                                | Tempo de propagação intrínseco do sinal através de uma porta lógica                                          |

(

#### **RESUMO**

Esta dissertação trata do projeto, construção e caracterização de circuitos integrados digitais de alta velocidade em Arseneto de Gálio, operando em taxas de gigabits por segundo. Circuitos digitais de alta velocidade são essenciais para melhorar o desempenho de computadores, sistemas de comunicação de alta capacidade, sistemas eletrônicos militares e de instrumentação. Circuitos integrados monolíticos em Arseneto de Gálio apresentam um bom compromisso entre consumo de potência e taxa de operação na faixa de gigabits por segundo, sendo uma solução para aplicações em alta velocidade.

Neste trabalho são apresentadas a principais famílias lógicas estáticas implementáveis a partir de transistores MESFETs de GaAs, bem como uma análise comparativa de suas características.

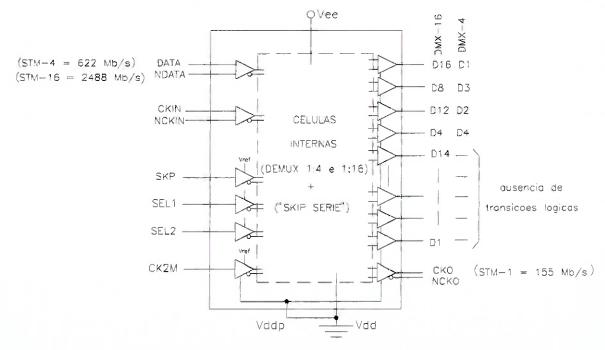

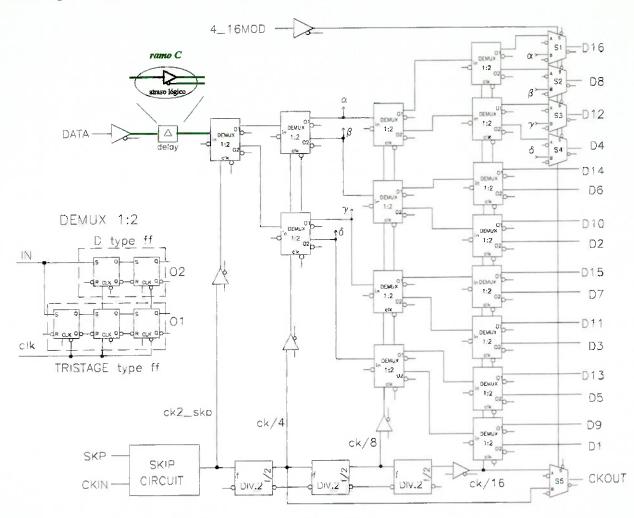

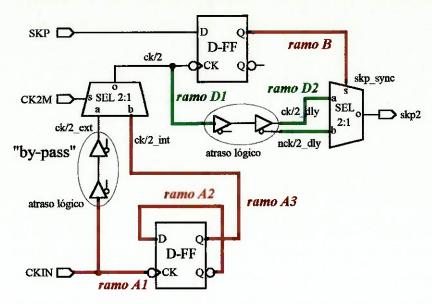

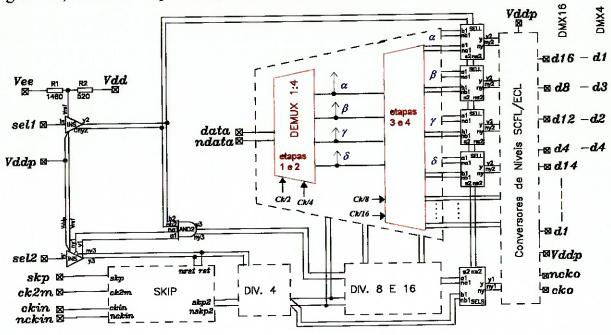

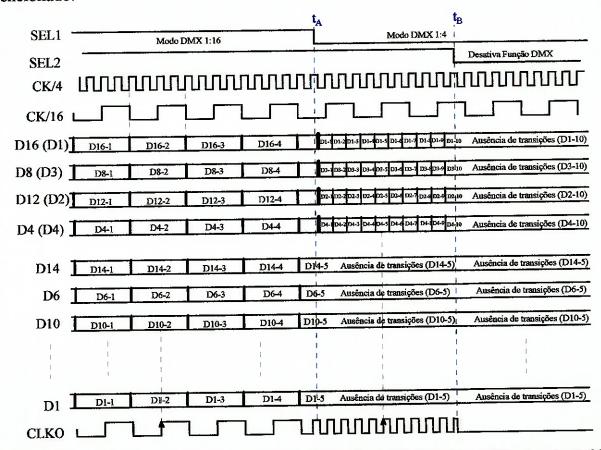

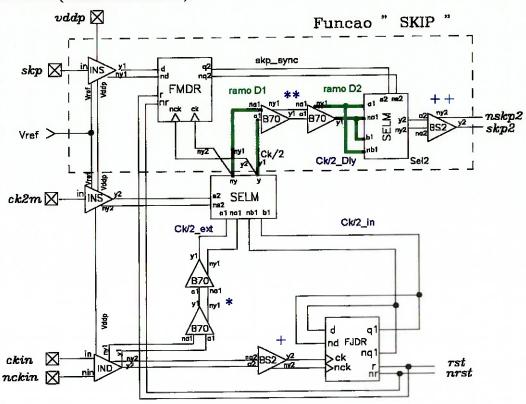

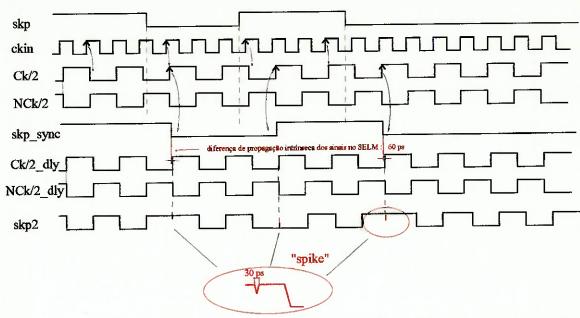

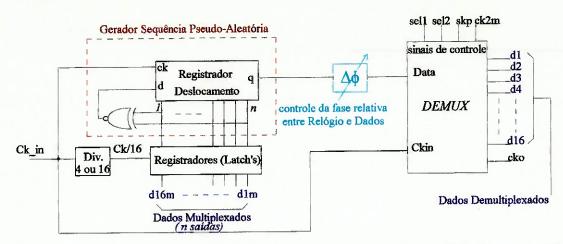

São abordadas as principais questões relativas ao projeto de circuitos integrados de alta velocidade através do projeto detalhado de um demultiplexador no tempo. O circuito foi projetado visando operar até 2,5 Gb/s com dois modos de demultiplexagem, 1:4 e 1:16, e integra um circuito rotacionador de bits de saída. Analisa-se as topologias desses dois tipos de circuito, apresentando-se o projeto de um demultiplexador empregando topologia tipo árvore com flip-flop tipo D e Tristage, a qual associa alta velocidade de operação e baixo consumo de potência. O circuito rotacionador de bits integrado ao demultiplexador utilizou uma topologia inédita, proposta a partir de modificações de circuitos encontrados na literatura.

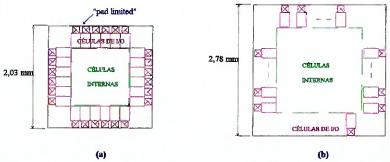

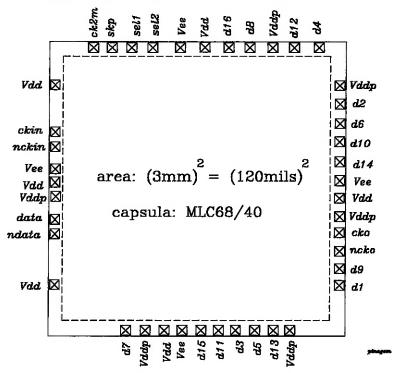

O circuito projetado foi construído utilizando-se um serviço de foundry de GaAs disponível comercialmente, empregando células padrão SCFL que usam transistores MESFETs com comprimento de porta de 1  $\mu$ m. A área total utilizada no processamento do circuito integrado foi de 2,78 x 2,78 milímetros quadrados.

São discutidas questões relativas à caracterização de circuitos integrados de alta velocidade, apresentando-se os resultados da caracterização do demultiplexador projetado.

O circuito construído demonstrou operar corretamente em ambos os modos de demultiplexagem até a taxa de 2,7 Gb/s, com consumo médio total de 1,4 W. Verificouse a correta atuação do circuito rotacionador de bits, comprovando-se a efetividade da topologia proposta.

As características do circuito integrado projetado demonstraram que o mesmo pode ser utilizado no processamento de sinais elétricos em sistemas de comunicações ópticas com padrões SDH e SONET.

(

#### "ABSTRACT"

The subject of this work is the design, construction and characterization of digital integrated circuits on Gallium Arsenide, operating at gigabits per second rates. High speed digital circuits are essential to improve the performance of computers, high capacity communication systems, military systems and instrumentation. Gallium Arsenide monolithic integrated circuits are a solution for high speed applications, presenting low power consumption at gigabits per second operating range.

This work presents the main static logic families employing GaAs MESFETs and a comparison among their characteristics. The main issues on the design of high speed digital integrated circuits are discussed and applied to the design of a demultiplexer circuit. This circuit was designed to operate up to 2.5 Gb/s as a 1:4 or a 1:16 demultiplexer and integrates a skip circuit. Topologies for high speed demultiplexer and skip circuits are analyzed and the design of a demultiplexer employing tree type architecture and D-type and Tristate flip-flops is presented in detail. The skip circuit was designed employing a new topology obtained modifying circuits presented in the literature.

The designed circuit was constructed using a commercially available foundry service based on a 1 micron MESFET technology. The design approach employed SCFL standard cells. The resulting chip area is 2.78 x 2.78 millimeters square.

Issues on characterization of high speed digital circuits are discussed and the experimental results of the demultiplexer are presented.

The circuit demonstrated correct operation in both 1:4 and 1:16 demultiplexing modes, operating up to 2.7 Gb/s with 1.4 W of power consumption. The correct operation of the skip circuit demonstrated the effectiveness of the circuit topology proposed in this work.

The performance of the demultiplexer with the integrated skip circuit allows its use on signal processing at optical communication systems using SDH and SONET standards.

### Capítulo 1 1. INTRODUÇÃO

(

(

(

(

(

(

(

#### 1.1 BREVE HISTÓRICO E APLICAÇÕES DE CI'S EM GaAS

Circuitos digitais de alta velocidade são componentes importantes na obtenção de melhores desempenhos em sistemas de comunicação, computadores, sistemas eletrônicos militares e instrumentação. Circuitos integrados baseados em substratos de Arseneto de Gálio, GaAs, aparecem como uma boa solução para aplicações de alta velocidade, apresentando a vantagem da baixa dissipação de potência em taxas de Gb/s.

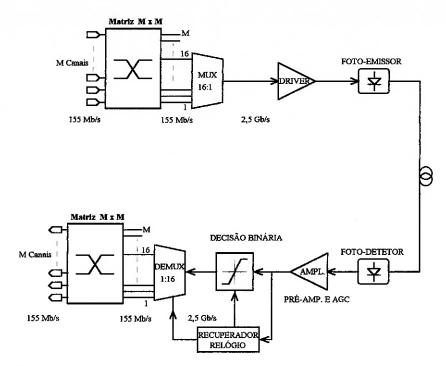

Particularmente, sistemas de comunicação ópticas com grande capacidade de transmissão de dados têm representado uma das áreas de ampla aplicação de CI's digitais de alta velocidade. O desenvolvimento destes sistemas foi estimulado pela necessidade crescente de comunicação em todo o mundo nos últimos anos. O sistema "Broadband Integrated Services Digital Networks", B-ISDN, é um exemplo de sistema de comunicação de alta capacidade com serviços de voz, dados e vídeo integrados, e portanto só pode ser implementado empregando canais físicos de elevada largura de banda de passagem, BW, como por exemplo a combinação de fibra óptica e circuitos digitais capazes de processar sinais em taxas de Gb/s. A figura 1.1 apresenta o diagrama de blocos simplificado para um sistema de comunicações por fibra óptica de longa distância em 2,5 Gb/s. Pode-se citar os seguintes circuitos elétricos integrantes do sistema: "laser driver", amplificador de transimpedância, chave "crosspoint". multiplexador, demultiplexador, deslocador de fase, circuito de decisão e recuperador de relógio. O exemplo mostra como combinar 16 canais independentes de 155 Mb/s em um único canal, multiplexado no tempo, com taxa de 2,5 G/s. Genericamente, ter-se-ia no transmissor um multiplexador de ordem de multiplexagem N com 2<sup>N</sup> entradas, onde N é inteiro, e, no receptor, um demultiplexador de mesma ordem de demultiplexagem, N. Ouando se adota a multiplexagem de canais no tempo, pode-se obter um ganho real de sistema devido à drástica redução do número de receptores, fibras ópticas, etc. Este ganho é ainda maior quando as distâncias entre transmissor e receptor são consideráveis, da ordem de centenas ou mesmo milhares de quilômetros.

Sistemas de comunicação ópticas têm-se mostrados bastante eficientes na transmissão de informação em taxas de Gb/s, além de apresentar inúmeras vantagens em relação aos sistemas de comunicação por microondas, como por exemplo imunidade a interferência eletromagnética e maior capacidade de transmissão de informação. Os padrões digitais de comunicação de mais alta capacidade SDH (Synchronous Digital Hierarchy), de origem européia, e o americano SONET (Synchronous Optical Network)

estão operando atualmente nas taxas de 2,5 e 10 Gb/s, sistemas STM-16, OC-48 e STM-64, OC-192, respectivamente.

Figura 1.1 Diagrama de blocos de um enlace óptico para comunicação a longa distância.

Historicamente, o primeiro circuito digital comercial em GaAs operando em Gigabits por segundo foi anunciado em 1983<sup>1</sup>, e o primeiro guia de circuitos em GaAs, incluindo circuitos digitais e analógicos, foi publicado em 1986<sup>2</sup>. Os primeiros CI's digitais em GaAs foram baseados na tecnologia MESFET, a qual ainda hoje é a tecnologia mais usada. Recentemente, projetos de CI's digitais de alta velocidade empregando dispositivos HEMT e HBT, baseados em heteroestruturas, têm sido largamente relatados, demostrando o potencial destas tecnologias emergentes na obtenção de taxas de operação mais altas<sup>3-5</sup>.

Já a disponibilidade de serviços externos de foundry em GaAs está permitindo aos projetistas acessar processos de fabricação bem estabelecidos. Assim, a tarefa desafiadora de desenvolvimento de CI's de alta velocidade em GaAs tornou-se mais viável. Algumas foundries de GaAs oferecem serviços de prototipagem multi-usuário de baixo custo, viabilizando as atividades de projeto de grupos de P&D, bem como as atividades de investigação acadêmica.

#### 1.2 OBJETIVOS DA DISSERTAÇÃO

Os objetivos dessa dissertação foram desenvolver capacitação em projeto, construção usando foundry externa e caracterização de CI's digitais de alta velocidade em GaAs.

Para a realização desses objetivos optou-se pelo projeto de um demultiplexador de sinais operando na faixa de 2,5 Gb/s, com características que permitisse seu uso em sistemas profissionais de comunicação óptica.

As especificações do demultiplexador e o suporte financeiro para a fabricação do mesmo foram fornecidos pelo CPqD da Telebrás.

A fim de atingir tais objetivos, foram realizados as seguintes atividades relacionadas a CIs digitais de alta velocidade em GaAs:

- estudo de famílias lógicas para taxas de Gb/s;

- estudo comparativo das diversas topologias de demultiplexadores;

- treinamento em ferramentas de projeto de CI's digitais: CADENCE EDGE (SOLLO 2000) e GDT V.5.2;

- realização de um projeto completo captura esquemática, simulação, leiaute e simulação pós-leiaute de um CI MSI empregando células padrão;

- emprego de técnicas de leiaute em altas taxas;

- uso de foundry externa na fabricação de um demultiplexador em GaAs;

- capacitação em medidas digitais de alta taxas (Gb/s).

- caracterização elétrica em taxas de Gb/s do CI MSI processado.

Na etapa de definição de objetivos considerou-se a possibilidade de realizar o projeto do demultiplexador ao nível de transistor. Obviamente, um projeto ao nível de transistor permite obter funções lógicas mais compactas, justamente pelo fato do usuário poder projetar células dedicadas segundo as necessidades do circuito, resultando muitas vezes em menor consumo de potência para o mesmo desempenho de velocidade. No entanto, optou-se por realizar o demultiplexador empregando-se células padrão de uma biblioteca pelas seguintes razões:

- ênfase do presente trabalho relaciona-se ao estudo de topologias de demultiplexadores e não à otimização de células básicas;

- as bibliotecas já contém portas lógicas otimizadas quanto a área, potência e taxa de operação;

- os dados referentes às células padrão permitem uma comparação realista entre topologias de demultiplexador, quando realizadas a partir da mesma tecnologia.

#### 1.2.1 Capacitação em projetos de alta velocidade

Tendo em vista a inserção do circuito em receptores ópticos, optou-se pelo desenvolvimento de um demultiplexador com taxa de operação estimada em 2,5 Gb/s com 16 canais de saída ou, alternativamente, em 622 Mb/s com 4 canais de saída, visando atender aos padrões de comunicação SDH STM-16 ou STM-4, e, equivalentemente, padrões SONET OC-48 ou OC-12. O CI projetado incluiu também um circuito de "skip" que permite deslocar os dados presentes nas saídas demultiplexadas para as saídas adjacentes, permitindo obter o correto alinhamento de quadro. Essa escolha foi motivada pelo interesse acadêmico em dominar técnicas de projeto e de caracterização de CI's digitais de alta velocidade em GaAs, conjuntamente aos objetivos do CPqD-Telebrás que, através dos contratos Telebrás-USP JDPqD 516/93 e JDPqD 586/94, financiou o processamento do CI em foundry externa e colocou à disposição equipamentos de medidas de taxas altas, necessários à realização da caracterização do CI.

O CI foi construído a partir de uma tecnologia de foundry comercialmente disponível, empregando-se MESFETs com comprimento de porta de 1 µm. Representa, até onde é de nosso conhecimento, o primeiro resultado de engenharia brasileira em projeto de CI de GaAs operando em taxas de Gb/s. Este trabalho aborda técnicas de projeto e de medidas de CI's digitais de alta velocidade em GaAs de média escala de integração (MSI).

Procurou-se desenvolver todas as etapas de projeto do CI demultiplexador, bem como habilitar-se para uso de foundry externa necessária ao processamento do circuito e, finalmente, realizar a caracterização do CI digital de alta velocidade.

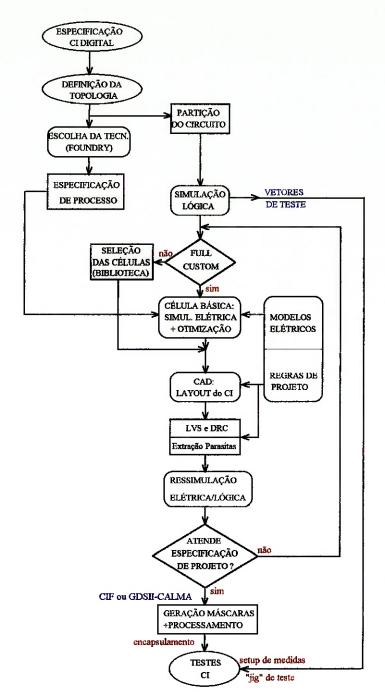

A figura 1.2 sintetiza as principais etapas de projeto e caracterização de um CI digital de alta velocidade em GaAs. O processo como um todo é similar àquele empregado em CI's de baixa taxa em Si. A diferença reside nos procedimentos de simulação e de leiaute que devem considerar os elementos parasitas das interconexões internas ao CI. Estes elementos parasitas afetam fortemente o desempenho do circuito em alta velocidade. A etapa de caracterização em alta velocidade requer cuidados especiais devido aos efeitos de parasitas associados às conexões e transições, presentes na "jig" de teste.

Figura 1.2 Fluxograma das principais etapas de projeto e caracterização de um CI digital de GaAs.

Neste esquema, parte-se de uma especificação funcional do circuito digital a ser projetado. Se este for demasiado complexo, deve-se fazer partições em sub-blocos funcionais menores. As características lógicas do circuito e da foundry selecionada determinarão se a abordagem de projeto será ao nível de transistor, ou baseada exclusivamente em células padrão de uma biblioteca já disponível, ou ainda uma abordagem mista que mescle as duas filosofias de projeto. Caso haja uma biblioteca de células padrão a qual possua todos as portas lógicas necessárias à implementação do circuito, então simulações lógicas serão suficientes para se garantir o desempenho desejado do circuito. Simulações elétricas adicionais serão necessárias caso o usuário

necessite otimizar novas células não disponíveis na biblioteca, para o caso de se empregar abordagem mista. Normalmente, são necessários algumas ressimulações elétricas e/ou lógicas para otimização do desempenho do circuito projetado. Após a realização do leiaute, devem ser extraídos os valores das capacitâncias e resistências parasitários, associados às interconexões que deverão ser considerados nas ressimulações pós-leiaute. Obtido finalmente o desempenho desejado, pode-se enviar para a foundry o arquivo que descreve o leiaute do circuito através de figuras geométricas, normalmente em formato GDSII-Calma ou CIF. Após o processamento, as amostras recebidas da foundry podem finalmente ser caracterizadas empregando técnicas e "jig" de teste de alta velocidade.

#### 1.2.2 Uso de Foundry Externa

A tarefa complexa e sofisticada de obtenção de um CI digital de alta velocidade, do projeto ao teste, pode ser subdivida em três fases: o projeto, o processamento e, finalmente, a caracterização do CI. O acesso a foundries externas de GaAs com processos de fabricação bem estabelecidos permite ao projetista obter circuitos no estado atual da arte, trabalhando apenas em técnicas de projeto e caracterização.

A disponibilidade de foundries externas que processam CI digitais de GaAs torna possível a formação de projetistas de CI de alta velocidade ao nível nacional. Mesmo porque existindo a opção de processamento onde vários usuários compartilham a mesma lâmina, a fabricação de CI em GaAs empregando foundry externa possibilita a redução dos custos de protótipos, viabilizando projetos de caráter experiemental e de investigação.

No entanto, o uso de foundry externa requer do projetista a adequação de seu ambiente de projeto ao da foundry, que envolve um amplo suporte de projeto para um determinado processo tecnológico, incluindo arquivos de descrição e de verificação de regras de projeto, arquivos de bibliotecas de elementos e células padrão e arquivos de modelos elétricos. Este suporte, em geral, está disponível somente para determinados softwares comerciais de projeto, o que pode, ocasionalmente, exigir do projetista um trabalho adicional de adaptação desses arquivos para outras ferramentas computacionais disponíveis.

Regra geral, são necessários 5 a 6 meses para se percorrer o ciclo completo de processamento de um CI em foundry externa na opção multi-usuário, do envio do leiaute do circuito ao recebimento das amostras encapsuladas.

#### 1.3 DESCRIÇÃO DO CONTEÚDO DOS CAPÍTULOS

Apresenta-se nos próximos capítulos considerações de projeto e resultados experimentais do demultiplexador de alta velocidade com circuito alinhador de bits proposto. No capítulo 2 são discutidas questões referentes ao desenvolvimento de CI's digitais de alta velocidade em GaAs, sendo abordados os ítens: comparação com outras tecnologias, principais famílias lógicas de alta velocidade atualmente implementáveis em GaAs e critérios de seleção de foundry externa.

No capítulo 3 é feita extensa análise comparativa das topologias de demultiplexadores e circuitos de "skip" encontrados na literatura à luz de critérios de excelência previamente estabelecidos.

O projeto do circuito integrando os dois modos de demultiplexagem e o rotacionador de bits de saída é descrito no capítulo 4. São feitas considerações de projeto e de leiaute do CI baseado no uso de células padrão tendo em vista a otimização do compromisso velocidade versus consumo de potência.

O capítulo 5 apresenta os resultados da caracterização elétrica das amostras do demultiplexador recebidas da foundry. Inicialmente são apresentados os principais parâmetros associados à caracterização de demultiplexadores com taxas de operação em Gb/s. Apresenta-se a seguir o setup de medidas e os resultados experimentais obtidos, comparando-os com os resultados das simulações lógicas do circuito projetado e com os resultados das principais publicações internacionais.

Finalmente, são apresentadas no capítulo 6 as conclusões e sugestões para trabalhos futuros, obtidas durante o processo de ordenação das idéias subjacentes ao período de realização deste trabalho.

#### Capítulo 2

#### 2. TECNOLOGIAS DE CI'S DIGITAIS DE ALTA VELOCIDADE

#### 2.1 INTRODUÇÃO

Nesta seção é feita uma breve comparação entre as tecnologias de GaAs e Si, destancando-se suas principais propriedades elétricas visando a construção de circuitos integrados de alta velocidade. A seguir, resume-se as características das famílias lógicas estáticas mais empregadas em GaAs. Classifica-se as estruturas lógicas de alta velocidade, do ponto de vista do tipo de transistor utilizado, dividindo-as em lógicas normalmente-ON ou normalmente-OFF. Finalmente, é feita uma avaliação das foundries de GaAs digitais existentes. São estabelecidos critérios para seleção de foundry, visando a escolha de uma foundry comercial para a realização da prototipagem do CI demultiplexador enfocado neste trabalho.

#### 2.2 COMPARAÇÃO COM A TECNOLOGIA DE SILÍCIO

A realização de CIs digitais empregando tecnologias de GaAs com potencialidades de alta velocidade e baixo consumo de potência apresenta certa dificuldade de obtenção, uma vez que é necessário obter simultaneamente:

- a) baixíssimos atrasos de propagação, τ<sub>pd</sub>,

- b) reduzido consumo de potência por porta lógica,  $P_{diss}$ ;

- c) produto consumo de potência-velocidade,  $P_{\text{diss}}.\tau_{\text{pd}}$ , reduzido;

- d) densidade de integração muito elevada, VLSI;

- e) maturidade e bom rendimento de processo tecnológico;

As tecnologias disponíveis de circuitos integrados rápidos baseadas em silício, a bipolar e a MOS, apresentam algumas vantagens de processo e material quando comparadas com a tecnologia GaAs<sup>6,7</sup>:

- fácil purificação;

- fácil formação de cristal;

- crescimento epitaxial bastante simples;

- alta integridade no crescimento do óxido, contribuindo para o aumento do rendimento.

Um dos principais compromissos feitos em projetos de CI's digitais refere-se ao desempenho da estrutura projetada em função do rendimento obtido. O rendimento global é definido como a fração dos chips que satisfazem aos critérios de desempenho

previamente especificado. Tanto o processo quanto o projeto do circuito afetam o rendimento global. O rendimento de processo envolve o controle de largura de linha, número de passos de máscaras, etc. É caracterizado simplesmente pela densidade de defeitos nas lâminas processadas. Já o rendimento de projeto, relaciona-se a escolha da topologia do circuito e à robustez de funcionamento do CI face às variações dos parâmetros do transistor. Um projeto lógico pode ser otimizado para funcionar sobre toda ou apenas uma porção do espalhamento dos parâmetros do processo de fabricação empregado.

Adicionalmente, existem mecanismos de processo tecnológico que possibilitam melhorar o desempenho de velocidade dos CI's. A tecnologia MOS tem se beneficiado destes mecanismos, uma vez que essa tecnologia encontra-se em fase bastante amadurecida. Primeiro, aumentando-se a tensão de alimentação e a excursão lógica, incrementa-se a transcondutância média dos dispositivos ativos, ou dito de outra forma, aumenta-se o produto ganho de corrente - faixa de passagem, obtendo-se a maximização da frequência de transição, f<sub>T</sub>, devido ao ponto de polarização do transistor. Finalmente, reduzindo-se a geometria dos dispositivos (MOS de canal curto) até o limite da resolução do processo foto-litográfico, além de se elevar a velocidade de operação, aumenta-se também o nível de integração. No entanto, surgem problemas quando se adota estes dois procedimentos. O aumento da tensão de alimentação traz aumento de consumo de potência e da energia dinâmica de chaveamento, a qual pode atingir níveis inaceitáveis para obtenção de circuitos com escala VLSI. Já o contínuo reescalonamento dos dispositivos atinge rapidamente o patamar de rendimento de processo inaceitável, resultando em custos e complexidade de processo elevados. Relatos na literatura para osciladores em anel construídos com tecnologia Si MOS submicrométrico apontam para desempenho excelente, com atrasos de propagação da ordem de 100 ps. No entanto, estes resultados não são reprodutíveis em escala comercial devido aos baixos níveis de rendimento e às altas energias de chaveamento associadas.

A emergência do GaAs como material de alto desempenho na obtenção de CI's de alta velocidade é resultado não apenas das suas propriedades básicas de semicondutor, mas também do compromisso favorável entre um grande número de aspectos, incluindo propriedades elétricas, implementação de dispositivos, faixa de temperatura de operação, tolerância à radiação, etc. O quadro 2.18 compara as principais características elétricas do Silício do Arseneto de Gálio para a realização de dispositvos eletrônicos e circuitos integrados, considerando temperatura ambiente.

Quadro 2.1 Carcterísticas elétricas do Arseneto de Gálio do Silício

| Propriedade Elétrica (@ Temp = 300 K)                           | Símbolo        | Unidade             | GaAs                 | Silício               |

|-----------------------------------------------------------------|----------------|---------------------|----------------------|-----------------------|

| Mobilidade elétrica (N = 10 <sup>17</sup> cm <sup>-3</sup> )    | $\mu_n$        | cm <sup>2</sup> /Vs | 5000                 | 800                   |

| Mobilidade das lacunas (N = 10 <sup>17</sup> cm <sup>-3</sup> ) | $\mu_p$        | cm <sup>2</sup> /Vs | 250                  | 350                   |

| Concentração intrínseca de portadores                           | n <sub>i</sub> | cm <sup>-3</sup>    | 9,0.10 <sup>6</sup>  | 1,45.10 <sup>10</sup> |

| Velocidade máxima de deriva do elétron                          | $V_d$          | cm/s                | 2.10 <sup>7</sup>    | 1.107                 |

| Campo elétrico crítico                                          | Ec             | V/cm                | 3.10 <sup>3</sup>    | 1.10 <sup>4</sup>     |

| Campo elétrico de ruptura                                       |                | V/cm                | 4.10 <sup>5</sup>    | 3.10 <sup>5</sup>     |

| Intervalo da banda de energia proibida                          |                | eV                  | 1,43                 | 1,12                  |

| Tipo de Intervalo de energia                                    | -              | -                   | direto               | indireto              |

| Densidade de estados na banda de condução                       |                | cm <sup>-3</sup>    | 5.10 <sup>17</sup>   | 3.10 <sup>19</sup>    |

| Resistividade máxima                                            | ρ              | Ω.cm                | ~109                 | ~105                  |

| Tempo de vida dos portadores minoritários                       |                | seg.                | 10 <sup>-8</sup>     | 1 <b>0</b> -3         |

| Altura da barreira Schottky                                     | фв             | V                   | 0,6-0,8              | 0,4-0,6               |

| Condutividade térmica                                           |                | W/cm.°C             | 0,46                 | 1,45                  |

| Coeficiente de dilatação                                        | ΔL/(L ΔΤ)      | °C-1                | 5,9.10 <sup>-6</sup> | 2,5.10 <sup>-6</sup>  |

| Permitividade Relativa                                          | ε <sub>r</sub> | •                   | 12,9                 | 11,7                  |

As principais vantagens do GaAs sobre o Si na obtenção de circuitos digitais de alta velocidade<sup>8</sup> são:

- Mobilidade elétrica do GaAs tipo n é cerca de 6 a 7 vezes mais alta que o Si. Portanto, tempos de trânsito da ordem de 5 a 10 ps, correpondendo a produtos ganho de corrente faixa de passagem entre 15 e 25 GHz podem ser obtidos para transistores com Lg entre 0,5 e 1,0 μm. Estes valores para o produto ganho-BW correspondem a uma melhoria de até 5 vezes sobre os dispositivos construídos a partir do silício;

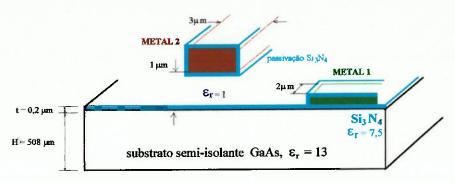

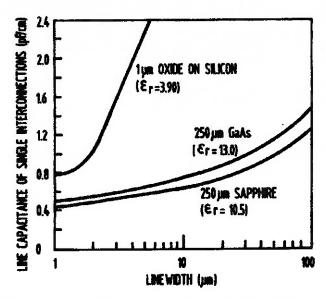

- Propriedade semi-isolante do substrato de GaAs (resisitividade na faixa de 10<sup>7</sup> a 10<sup>9</sup>

Ω.cm para temperatura ambiente) é outra vantagem que permite a simplificação

tecnológica e otimização de desempenho: não apenas minimiza as capacitâncias

parasitárias para o plano terra como proporciona também a fácil isolação elétrica de

dispositivos em um mesmo substrato;

- GaAs possui faixa de operação de temperatura mais ampla que o Si, entre -200 °C a +200 °C devido ao intervalo de energia mais amplo do GaAs. Além disto, o GaAs apresenta-se mais resistente à radiação devido à ausência de óxido de porta;

- Barreira Schottky pode ser realizada em GaAs a partir de uma ampla variedade de metais (Al, Pt, Ti, ...); obtém-se junções schottky de ótima qualidade associada a fatores de idealidade, n, menores que 1,1 e baixíssimas correntes reversa, J<sub>S</sub> < 1 μA/cm<sup>2</sup>. Fatores de idealidade excelentes permitem a realização de MESFETs com

características bem controladas.

• Intervalo de energia com transição direta entre as bandas de valência e de condução permite a recombinação radioativa eficiente de elétrons e lacunas, possibilitando que junções pn diretamente polarizadas possam ser empregadas na construção de emissores de luz; obtém-se com isto a integração eficiente de funções elétricas e ópticas.

Por outro lado, a tecnologia GaAs apresenta limitações de realização de circuitos que empreguem simultaneamente transistores tipo n e p, devido à baixa mobilidade de lacunas em relação aos elétrons, contrariamente ao que ocorre em circuitos CMOS de Si. Assim, muitas das estruturas de circuitos lógicos empregadas em Si não podem ser adaptadas para GaAs. Outro problema encontrado na tecnologia GaAs está associado à obtenção de elevados níveis de integração de dispositivos (VLSI e ULSI), uma vez que as caracteríticas térmicas e também mecânicas do GaAs são inferiores às do Si. A condutividade térmica do GaAs é três vezes menor que a do Si, apresentando problemas de dissipação de potência quando o nível de integração cresce excessivamente. Por sua vez, o coeficiente de dilatação do GaAs é cerca de duas vez maior que o do Si, que associado à pior condutividade térmica resulta em delicados problemas de montagem. Além disto, os procedimentos de fabricação em GaAs devem levar em conta a grande fragilidade do substrato, devido às pequenas espessuras, tipicamente entre 100 e 300 μm. Estes fatores são alguns dos que influenciam na obtenção de um menor rendimento de processo de fabricação na tecnologia GaAs.

Por sua vez, o Si apresenta limitações quando se trata de aplicações de alta velocidade. Atualmente, estas aplicações estão divididas em dois campos:

- computadores ultra-rápidos, com ciclos de máquina abaixo dos nanosegundos;

- sistemas de telecomunicações e de instrumentação em taxas de multi-Gigabit/s.

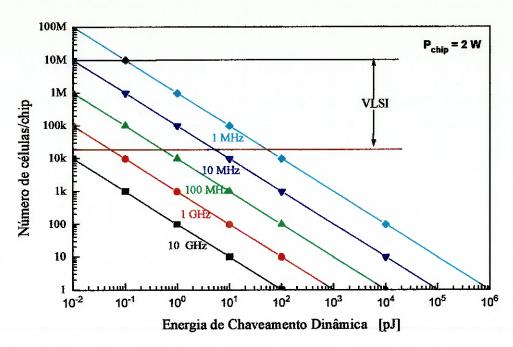

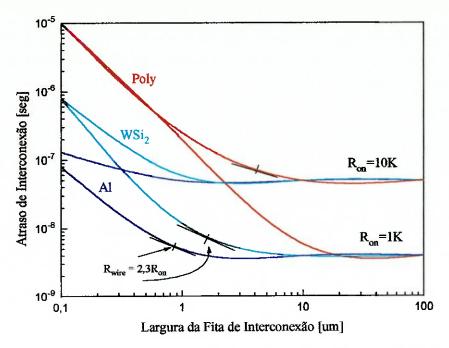

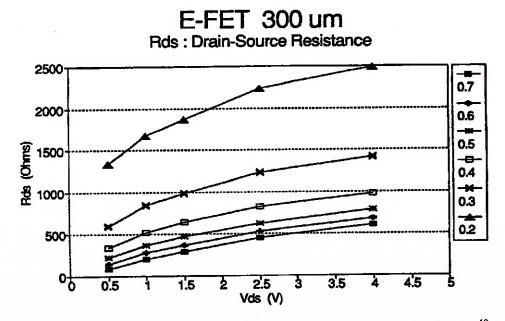

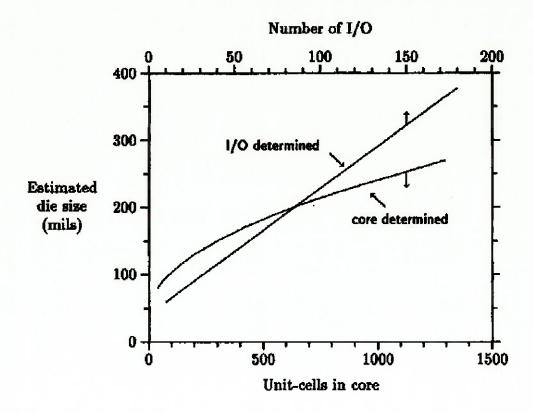

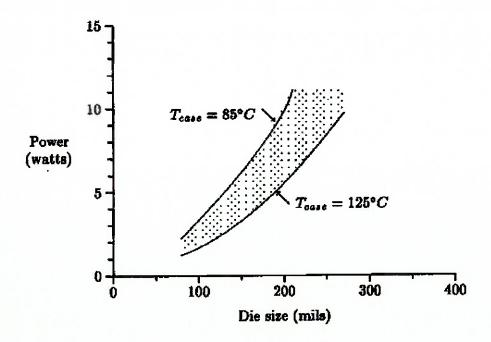

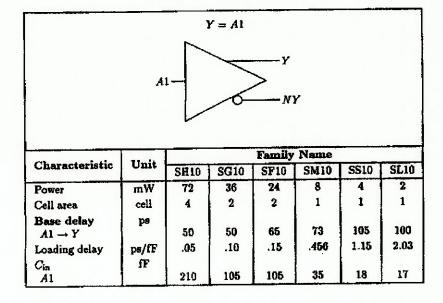

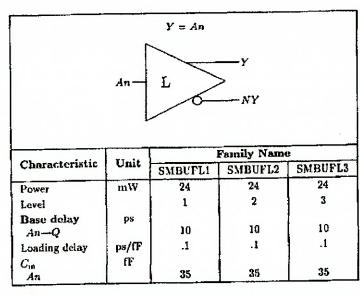

A primeira classe de aplicações de alta velocidade requer circuitos com níveis de integração muito alto, VLSI, e a segunda, níveis de integração alto, LSI. Uma tecnologia para circuitos digitais de alta velocidade com escala de integração elevada e muito elevada deve satisfazer os requisitos de integração, alto rendimento de processo e baixíssima energia dinâmica de chaveamento. Esta energia é definida como sendo a mínima energia necessária para se obter o chaveamento entre níveis lógicos considerando um ciclo de relógio, sendo dado pelo produto potência dissipada - atraso, 2.P<sub>diss</sub>.τ<sub>pd</sub>. O requisito de baixa energia dinâmica de chaveamento é bastante severo: energias menores que 0,1pJ são fundamentais para se obter circuitos VLSI de alta velocidade. A figura 2.1<sup>7</sup> mostra os limites entre a energia dinâmica de chaveamento e o número de portas lógicas por chip para um caso realístico de potência dissipada pelo chip de 2 W.

Figura 2.1 Limite para a obtenção de circuitos VLSI em função da energia dinâmica de chaveamento, considerando-se caso prático de  $P_{diss} = 2W$ .

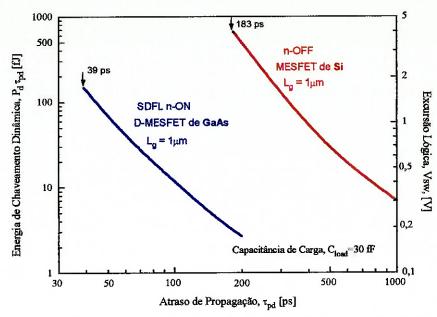

Fazendo-se uma comparação entre portas lógicas implementadas em tecnologias de Si e de GaAs verifica-se também a superioridade de desempenho em alta velocidade do GaAs, em termos de energia dinâmica de chaveamento. A figura 2.2 apresenta a energia dinâmica de chaveamento calculada<sup>7,9</sup> para portas lógicas normalmente-ON e família SDFL em GaAs, em função do atraso de propagação, comparando-as com portas normalmente-OFF em Si. Note que em ambos os casos são considerados MESFETs de W=10μm, L=1μm e capacitância de carga nas saídas das portas igual a 30 fF. Obtém-se, evidentemente, uma drástica redução da energia mínima necessária ao chaveamento, bem como do produto potência-velocidade, quando se emprega MESFET's de GaAs. Assim, velocidades de chaveamento da ordem de 4 a 6 vezes maiores são obtidas com transistor MESFET de GaAs, para a mesma excursão lógica. O melhor desempenho das portas implementadas com MESFET's de GaAs seria ainda mais acentuado se ambas as portas lógicas empregassem transistores do tipo enriquecimento. Como será discutido no próximo ítem, portas lógicas n-OFF necessitam de menor energia de chaveamento.

Assim, conclui-se pelo potencial de desempenho superior das portas lógicas de alta velocidade realizadas a partir de tecnologias em GaAs. CI's empregando FET's de GaAs têm demonstrado ser mais rápidos que os CI's de tecnologias MOS e bipolares de homojunção de Si, ou, alternativamente, exibem menor consumo de potência para a mesma taxa de operação.

Figura 2.2 Desempenho de chaveamento de portas lógicas implementadas a partir de MESFET's de Si e GaAs para a mesma capacitância de carga.

#### 2.3 FAMÍLIAS LÓGICAS QUE EMPREGAM MESFET EM GaAs

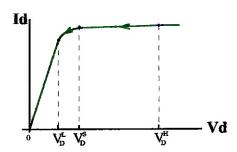

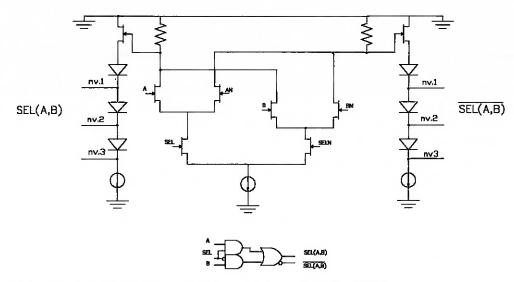

Existem inúmeras famílias lógicas $^{7,10-16}$  implementáveis em GaAs. Todas elas podem ser classificadas, basicamente, em duas abordagens construtivas: portas lógicas normalmente-ON e normalmente-OFF. Portas lógicas normalmente-ON são construídas empregando-se apenas transistores do tipo depleção, D-FETs ( $V_{th} < 0$ ) e foram, historicamente, a primeira geração de dispositivos desenvolvidos para circuitos digitais de GaAs. Isto foi devido à maturidade de processo dos D-FETs. Mais tarde, quando o rendimento de processo e a uniformidade da tensão de limiar,  $V_{th}$ , dos transistores do tipo enriquecimento, E-FETs ( $V_{th} > 0$ ), foram suficientemente aperfeiçoados, introduziu-se as portas lógicas normalmente-OFF. Estas são construídas empregando-se D-FETs e E-FETs, detendo características essenciais para a implementação de circuitos LSI e VLSI em GaAs, i.e., área reduzida e baixa energia dinâmica de chaveamento.

O projeto de uma porta lógica em GaAs deve incluir as seguintes etapas<sup>14</sup>:

- definição da configuração da porta: normalmente-ON ou -OFF;

- otimização das características estáticas da porta: curva de transferência, margem de ruído, etc, objetivando garantir operação correta da função implementada para as condições de pior caso de variação de processo e temperatura;

- otimização das características dinâmicas: velocidade, potência, dependência de fan-in e fan-out, etc.

- minimização da área de leiaute.

A otimização global do projeto de uma porta lógica depende do compromisso entre todos esses parâmetros. No caso de projeto das portas lógicas em GaAs, a otimização é feita quase sempre visando atingir máxima velocidade, ou em alguns casos, minimização do consumo de potência.

Uma porta lógica estática em GaAs é sempre constituída por um bloco lógico com *i* entradas (FI), conectadas a uma fonte de alimentação através de uma carga. Este bloco é essencialmente um amplificador de tensão. Segue-se então um amplificador buffer com impedância de saída muito baixa, que fornece maior corrente de saída, ampliando a capacidade de fan-out da porta. Deve ser capaz de alimentar *j* portas (FO), conectadas em paralelo na saída. Em algumas famílias lógicas, este bloco desempenha também alguma função lógica, ou mesmo atua como deslocador de nível de tensão em portas lógicas normalmente-ON.

Como em Si, portas lógicas construídas em GaAs podem ser estáticas ou dinâmicas. Esta última, também chamada de porta lógica de transferência, emprega o FET como transistor de passagem, estando atualmente em fase de desenvolvimento. Exemplos de lógicas dinâmicas em GaAs são: a) TTDL (Tricke Transistor Dynamic Logic), b) SPDL (Split Phase Dynamic Logic) c) TDFL (Two Phase Dynamic FET Logic) d) DPTL (Differencial Pass-Transistor Logic) e) CCDL (Capacitively Coupled Domino Logic). No entanto, as lógicas dinâmicas não são objetos deste trabalho e portanto não serão abordadas.

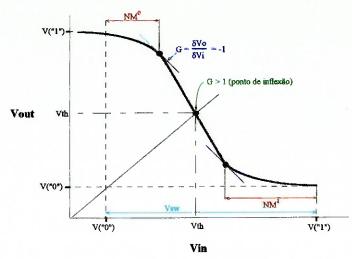

A margem de ruído em uma porta lógica, NM, é definida<sup>11</sup> a partir de sua curva de transferência,  $V_{out} \times V_{in}$ , como apresentado na figura 2.3. Usualmente, a margem de ruído é dada pelo intervalo de tensão de entrada, medido entre o ponto de operação, V("0") ou V("1"), e o ponto de intersecção com a reta de inclinação  $G = \frac{dVo}{dVi} = -1$ , i.e., a reta correspondente ao ganho unitário. Duas outras definições comumente empregadas para NM substituem os pontos de ganho unitário da definição anterior por a)aqueles onde as tensões se saída atingem 10% e 90% do valor da excursão lógica,  $V_{SW}$ , ou ainda b)os pontos de intersecção da reta tangente ao ponto de inflexão (G > 1) com os níveis de saída "0" e "1".

Observe-se que dependendo do ponto de operação escolhido, V("0") e V("1"), determina-se valores de margem de ruído associado aos pontos de operação,  $NM^0$  e  $NM^1$ , distintos. Para maximizar a margem de ruído, i.e.,  $NM^0 = NM^1 = NM$ , deve-se fazer  $V_{th}$  no ponto médio da excursão lógica,  $V_{SW}$ , i.e.,:

$$V_{th} = \frac{V("0") + V("1")}{2} \tag{2.1}$$

Figura 2.3 Curva de transferência DC para um inversor genérico, mostrando um dos critérios para obtenção da margem de ruído.

Uma vez que a geração do ruído interno à porta lógica aumenta com o incremento da excursão lógica, o parâmetro imunidade a ruído, NI, de uma porta ou mesmo de uma família lógica, é empregado muitas vezes para se comparar o desempenho de circuitos distintos. A imunidade de ruído pode ser expressa por<sup>11</sup>:

$$NI = \frac{min\{NM^{1}, NM^{0}\}}{V_{SW}}$$

(2.2)

O projeto otimizado de uma porta lógica deve ter como especificação uma corrente de carga menor que a corrente máxima através do transistor driver de saída. Esta condição pode ser expressa pelo ganho linear da porta lógica nas proximidades de  $V_{th}$ : deve-se ter G>1. Com isto, em uma sequência de células lógicas cascateadas permite-se que algumas portas sucessivas apresente ganho global ligeiramente menor que 1. Neste caso, basta restaurar o ganho através de um estágio fortemente regenerativo, obtendo-se G>1.

A margem de ruído maximizada está relacionada à excursão lógica e ao ganho linear ao redor de  $V_{th}$  (assumindo G>1) da porta lógica através de  $^{14}$ :

$$NM^{0} = NM^{1} = \frac{V_{SW}}{2}.(1 - \frac{1}{G})$$

(2.3)

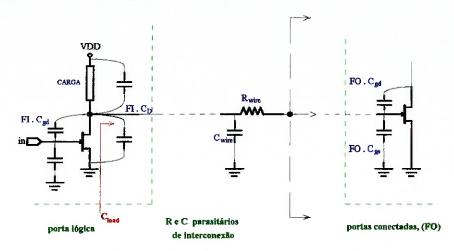

Por outro lado, a operação em alta velocidade restringe o ganho a valores baixos, tipicamente da ordem de G = 2, uma vez que a capacitância de carga na saída da porta lógica, figura 2.4, é composta por  $^{14}$ :

$$C_{load} = C_{wire} + FI \left[ C_{gd} (1 + 1/G) + C_D \right] + FO \left[ C_{gs} + C_{gd} (1 + G) \right]$$

(2.4)

onde: (1 + 1/G) : efeito Miller da capacitância de entrada para a saída

(1 + G) : idem, de saída para a entrada

#### C<sub>D</sub> : capacitâncias associadas ao dreno

com G > 1, então o ganho não pode ser muito grande, pois resultaria em  $C_{load}$  elevado, o que é incompatível com operação em alta velocidade.

Figura 2.4 Componentes da capacitância C<sub>load</sub> em uma porta lógica.

A exigência de baixos ganhos implica no conhecimento e controle de todas as fontes de ruídos lógicos. Assim, preocupação bastante pertinente ao projeto de portas lógicas rápidas refere-se à identificação e caracterização das fontes de ruído associadas ao circuito, são elas: cross-talk entre portas independentes, correntes transientes presentes nas linhas de alimentação e as não-uniformidades de processo tecnológico. Estes fatores podem causar variação no desempenho da porta, ou mesmo operação imprópria. Como regra geral, a somatória instantânea para o pior caso das amplitudes de todos os ruídos deve ser menor que a margem de ruído da porta lógica, afim de que o ruído não provoque comutação de estado lógico da porta lógica.

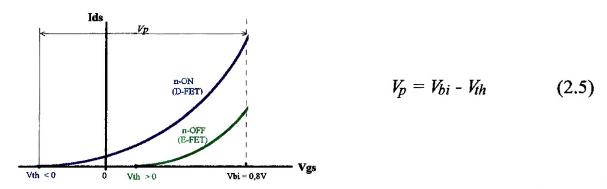

$\label{eq:Vale ressaltar} Vale \ ressaltar \ ainda \ aqui \ a \ relação \ utilizada \ para \ a \ tensão \ de \ limiar \ de \ condução \ do \ transistor, \ V_{th}, \ e \ a \ tensão \ de \ pinch-off, \ V_p, \ dado \ por:$

Figura 2.5 Relação entre a tensão de limiar, de pinch-off e built-in para transistores E-e D- FETs.

#### 2.3.1 Portas lógicas Normalmente-ON

Um grande número de familias lógicas tem sido proposto empregando-se FETs que operam em modo depleção, D-FET. As mais exploradas têm sido: Buffered FET Logic (BFL), Schottky Diode-FET Logic (SDFL) e Capacitor-Coupled FET Logic (CCFL). Em geral, famílias lógicas que empregam apenas transistores normalmente-ON necessitam de duas fontes de alimentação. A fonte negativa alimenta o estágio de saída, que por sua vez fornece nível de tensão negativo, necessário para se obter o corte do D-FET de entrada da próxima porta. Tensão de limiar para as famílias normalmente-ON estão na faixa de -3,0 a -0,5V.

#### Buffered FET Logic (BFL)

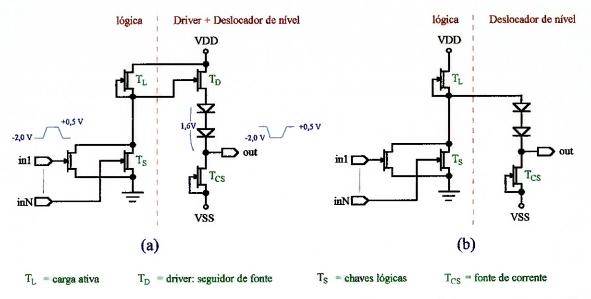

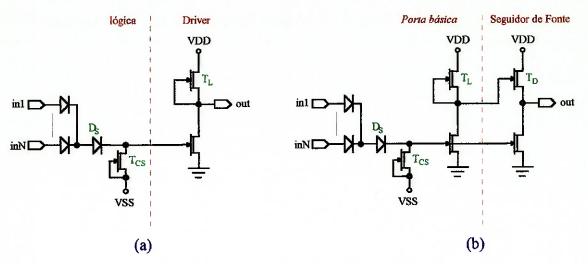

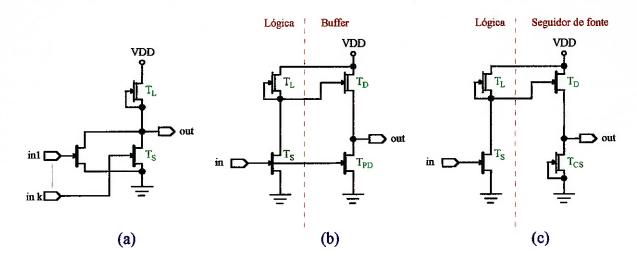

A estrutura básica para uma porta lógica BFL é mostrada na figura 2.6.a. Consiste de duas secções: lógica de entrada e driver / deslocador de nível de saída. Pode-se implementar diferentes funções lógicas modificando-se a configuração dos transistores da secção lógica de entrada, quer seja colocando mais transistores em paralelo (NOR), quer seja colocando-os em série (NAND). A combinação de transistores série e paralelo em uma mesma porta originará funções lógicas combinatórias mais complexas. Já os estágios driver / deslocador de nível de saída garantem aumento substancial na capacidade de fanout e compatibilidade de nível lógico de entrada e saída entre portas lógicas. Esta estrutura emprega fonte de alimentação negativa,  $V_{\rm SS}$ , com o objetivo de obter o chaveamento OFF dos D-FETs ( $T_{\rm S}$ ) da próxima porta lógica conectada à saída, incrementando o nível de complexidade da porta. A tensão de limiar dos D-FETs está está na faixa de -2,5 <  $V_{\rm th}$  < -1,0 V, e os níveis lógicos "1" = +0,5 V, e "0" = -2,0 V.

Assim, a família lógica BFL emprega um número razoavelmente grande de transistores por porta, tornando-a inviável para projetos VLSI. Por outro lado, a estrutura BFL é considerada uma das mais rápidas, embora esta velocidade seja obtida justamente às custas de área e de consumo de potência do elevados. Como exemplo, portas lógicas BFL empregando MESFET de  $L_g=1~\mu m$  e  $f_T=15~GHz$  apresentaram atraso de propagação intrínseco da ordem de  $\tau_{pd}=60~ps$  para um comumo de potência de  $12mW^{17}$ . Ou ainda, atrasos de propagação da ordem de  $\tau_{pd}=34~ps$  foram relatados em portas BFL com  $P_{diss}=41~mW$  e  $L_g=0,5~\mu m$ .

A maior parte desta potência é dissipada no estágio driver de saída. Portanto, é possível obter uma versão de consumo de potência reduzido para a estrutura BFL eliminado-se o transistor de carga do estágio driver, T<sub>D</sub>, como mostrado na figura 2.6.b.

Esta nova configuração é denominada às vezes LBFL (Low Power Buffered FET Logic), ou às vezes UFL (Unbuffered FET Logic), sendo aplicável a projetos de complexidade LSI. A tensão de limiar da lógica LBFL,  $V_{th}$ , é aumentada de -2,5V, no caso da porta BFL, para -1,0V, resultando em uma potência consumida reduzida,

tipicamente 5 mW/porta. No entanto, a ausência de  $T_D$  reduz significamente a capacidade de fan-out e a velocidade da porta.

Outra limitação da estrutura LBFL refere-se à necessidade de maior controle no desvio de V<sub>th</sub> ao longo da lâmina, o que só é obtido com processos tecnológicos maduros e bem estabelecidos, com os quais são então possíveis obter transistores E-FETs com características estáveis e reprodutíveis.

Figura 2.6 a. Porta BFL b. Porta LBFL ou UFL, sem o driver seguidor de fonte.

Schottky Diode-FET Logic (SDFL)

Nesta abordagem de projeto de portas rápidas são empregados diodos schottky na implementação da função lógica OR. Uma possível configuração é apresentada na figura 2.7.a. O diodo D<sub>S</sub> provê um deslocamento de nível de tensão; finalmente, um estágio buffer é acrescentado com o objetivo de se obter ganho de corrente maior que 1. A estrutura SDFL básica apresenta menor consumo de potência e área que a BFL, devido à substituição dos transistores de entrada pelos diodos schottky, de área reduzida, mas com menor velocidade e capacidade de fan-out.

É possível, no entanto, aumentar a capacidade de fan-out de uma porta através do acréscimo de um estágio seguidor de fonte push-pull na saída, como mostrado na figura 2.7.b.

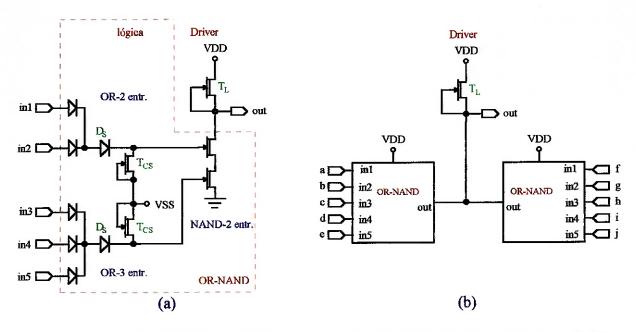

Os diodos schottky empregados para a realização da função OR de entrada são de alto desempenho. Se a função combinatória é mais complexa e/ou for a função NAND, será implementada em dois níveis lógicos, como visto na figura 2.8.a. Uma porta SDFL com 3 níveis lógicos de complexidade é necessária para implementar a função OR-NAND/Wired-AND, figura 2.8.b. Portanto, a estrutura SDFL apresenta a seguinte característica de conectividade na realização das funções lógicas:

. apresenta fan-in virtualmente ilimitado para o primeiro nível lógico;

- . para o segundo nível, fan-in está limitado a 2 ou 3;

- . por razões de realização, fan-in no terceiro nível lógico está limitado a 2.

Figura 2.7 a. Porta SDFL básica

b. Porta SDFL com estágio seguidor de fonte.

Figura 2.8 a. OR-NAND em SDFL

b. OR-NAND/Wired-AND em SDFL.

Capacitor-Coupled FET Logic (CCFL).

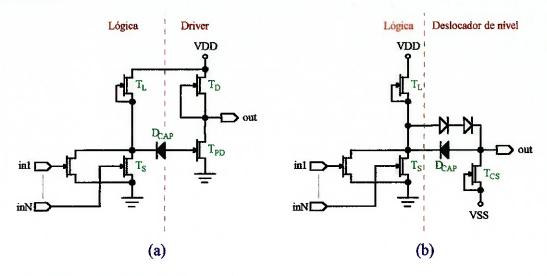

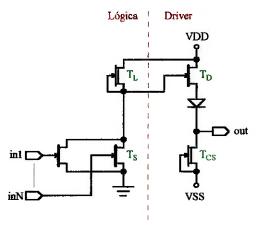

A lógica de transistor acoplado através de capacitor permite eliminar a necessidade de diodos deslocadores de nível em portas normalmente-ON. A figura 2.9.a apresenta uma porta CCFL típica, onde um diodo reversamente polarizado é empregado como capacitor,  $D_{CAP}$ , no acoplamento interestágio.

Obtém-se nesta configuração redução de potência consumida em relação à família BFL e SDFL, uma vez que não há dissipação de potência nos capacitores. Além disto, como o capacitor é colocado em série com a porta do transistor  $T_{PD}$ , a capacitância de

carga é reduzida e portanto a velocidade da porta lógica é melhorada. Esta configuração admite enorme faixa de variação na tensão de limiar. Foi reportado corretamente em 1GHz com variações de tensão de limiar de -4,0 <  $V_{th}$  < -0,5 V na mesma lâmina.

D<sub>CAP</sub> = diodo reversamente polarizado (capacitor)

Figura 2.9 a. Porta CCFL b. Porta CDFL.

No entanto, o uso de capacitor implica em uma frequência operacional mínima para o circuito, determinada basicamente pelas correntes de fuga, pelo tamanho relativo do capacitor de acoplamento e pela polarização reversa porta-fonte do transistor T<sub>PD</sub>. Para tornar ótima a eficiência de transferência da porta lógica, deve-se ter capacitâncias de polarização reversa elevadas. Para um inversor, a área ocupada pelo diodo representa aproximadamente 40 % da área total do circuito. Tipicamente, a frequência mínima de operação é de alguns KHz. Em aplicações onde não é aceitável a existência de uma frequência de corte inferior, pode-se combinar a polarização reversa e direta de diodos objetivando o deslocamento de nível de tensão e o acoplamento capacitivo interestágio. A figura 2.9.b mostra tal configuração, denominada Capacitor-Diode FET Logic (CDFL). A desvantagem desta estrutura em relação à porta CCFL é um aumento da área, resultado da adição dos diodos deslocadores de nível, embora possa ser mantido um baixo consumo de potência.

## 2.3.2 Portas lógicas Normalmente-OFF

Portas lógicas normalmente-OFF em GaAs tornaram-se viáveis somente em meados da década de 80, devido ao aperfeiçoamento dos processos tecnológicos, particularmente, pela redução do desvio máximo da tensão de limiar ao longo da lâmina e de sua reprodutibilidade de lâmina para lâmina. Complementarmente, algumas famílias normalmente-OFF foram propostas visando minimizar a dependência de seu desempenho (funcionamento e margem de ruído) em relação às variações de V<sub>th</sub>. Este tipo de porta

utiliza FETs de enriquecimento, E-FETs, como dispositivo de chaveamento e D-FETs como carga ativa, fonte de corrente, etc. Necessitam geralmente de apenas uma única fonte de alimentação para obter o mesmo desempenho dinâmico que a maior parte das famílias normalmente-ON. Incluem-se aqui as famílias Quasi-FET Logic (QFL), Direct-Coupled FET Logic (DCFL) e Source Coupled FET Logic (SCFL).

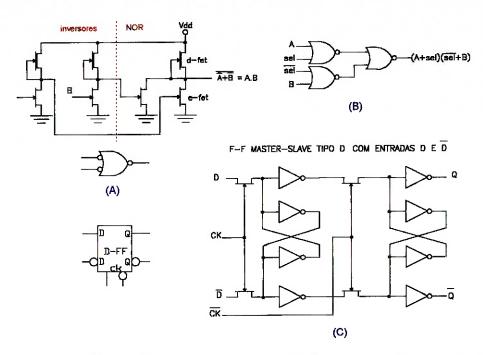

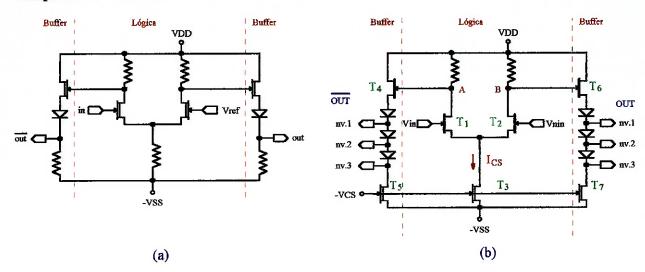

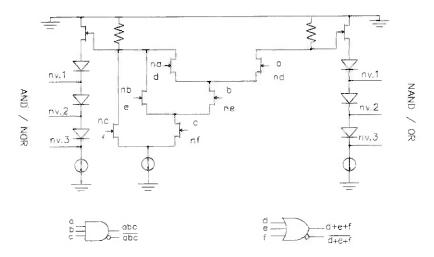

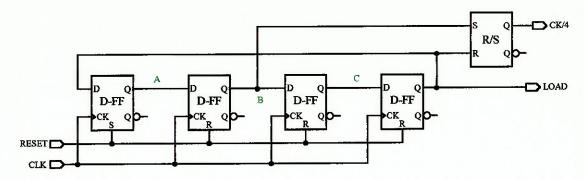

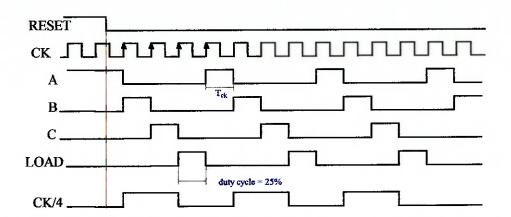

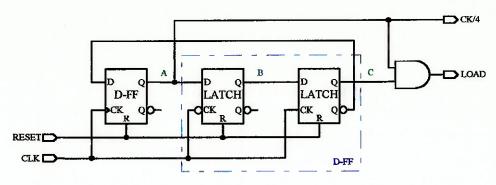

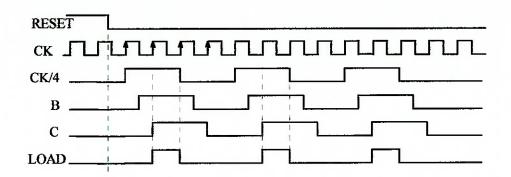

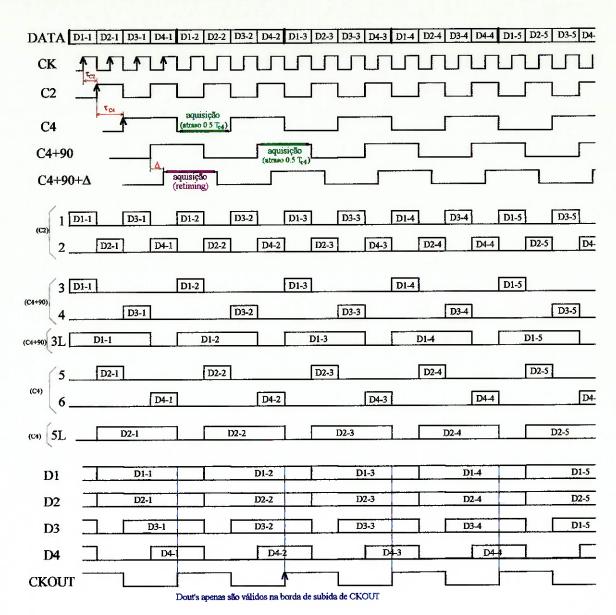

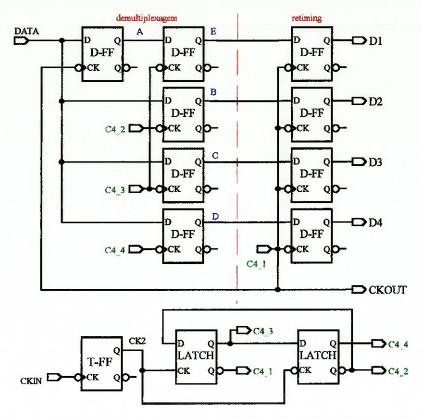

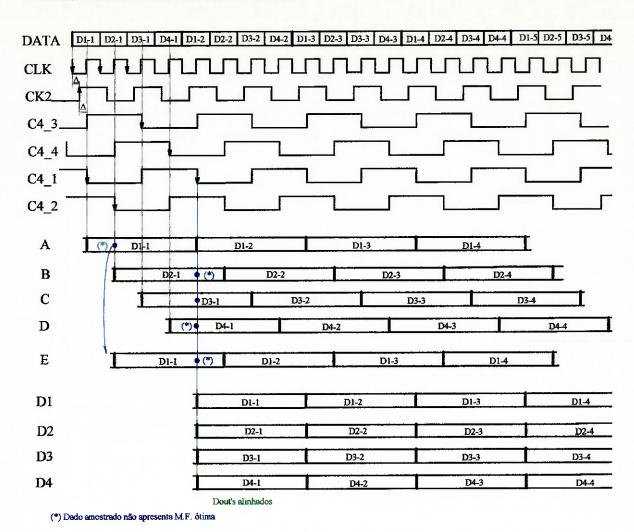

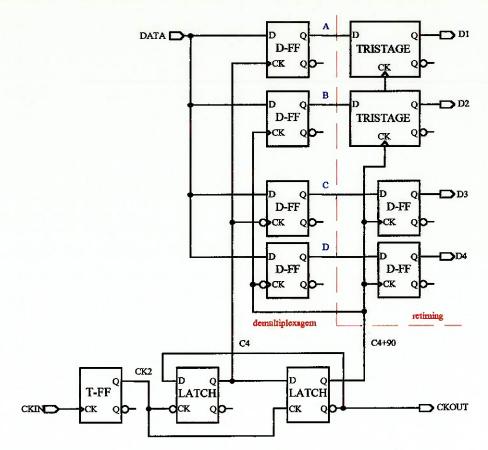

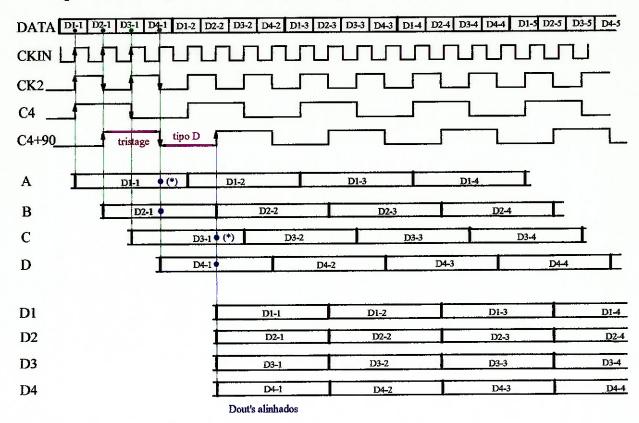

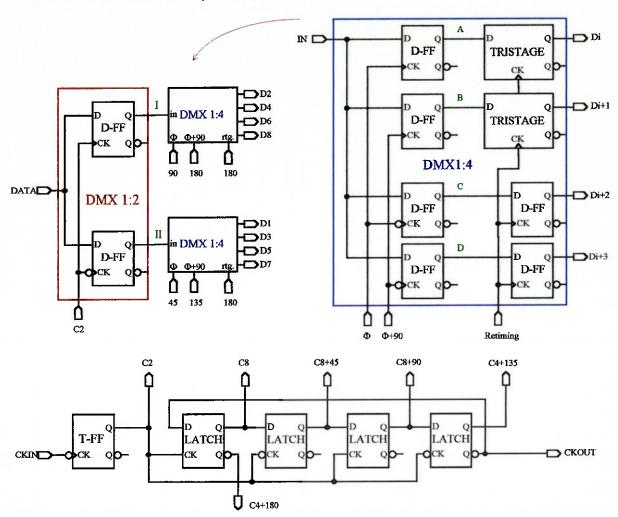

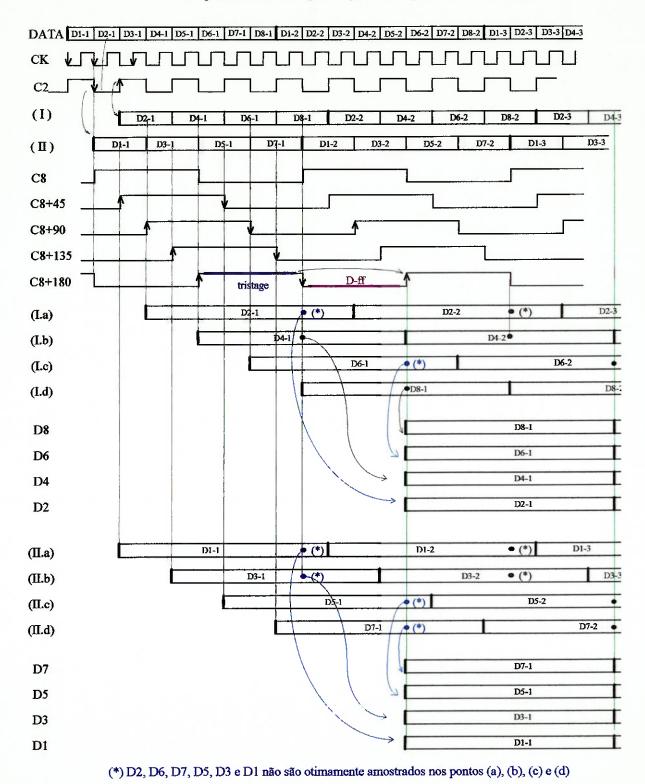

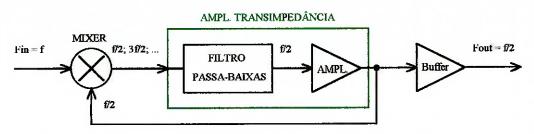

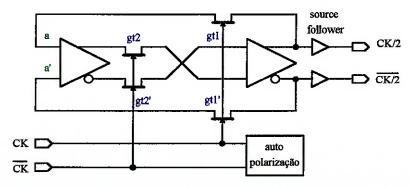

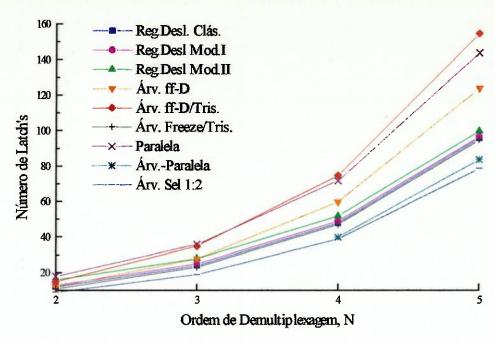

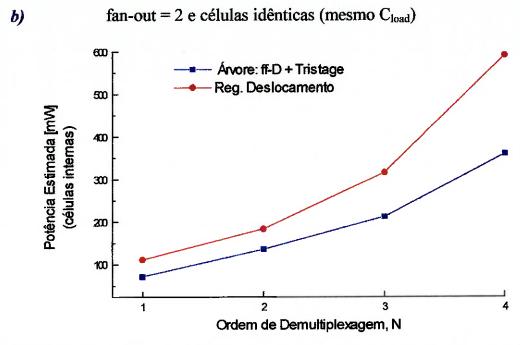

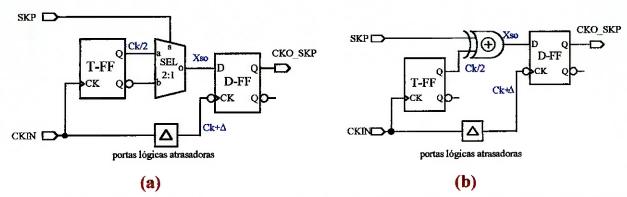

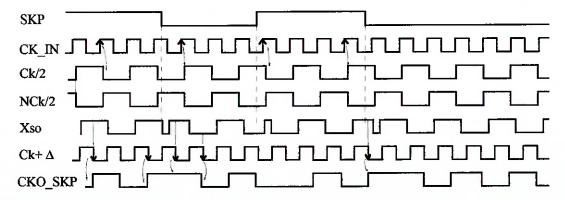

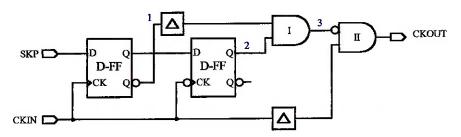

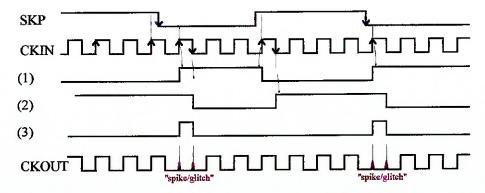

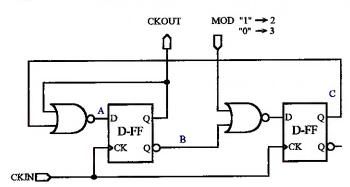

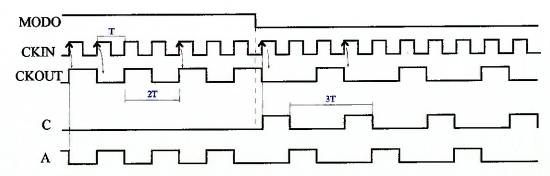

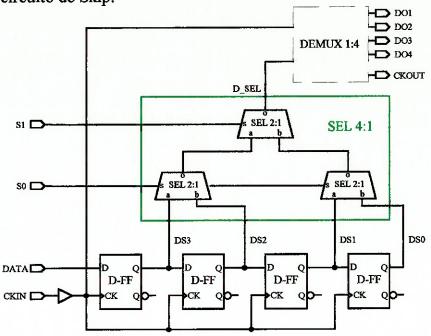

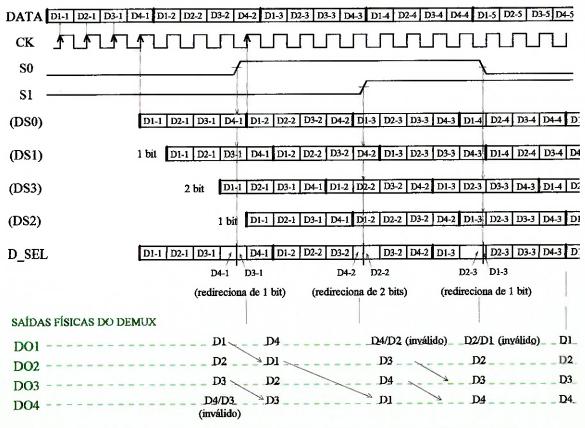

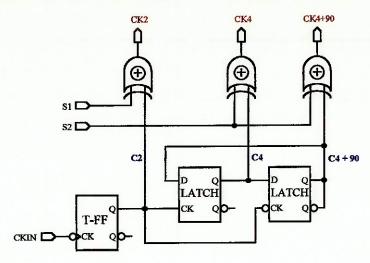

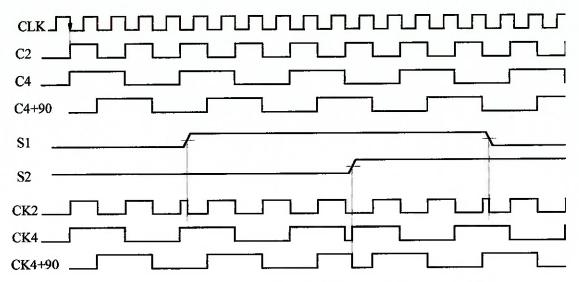

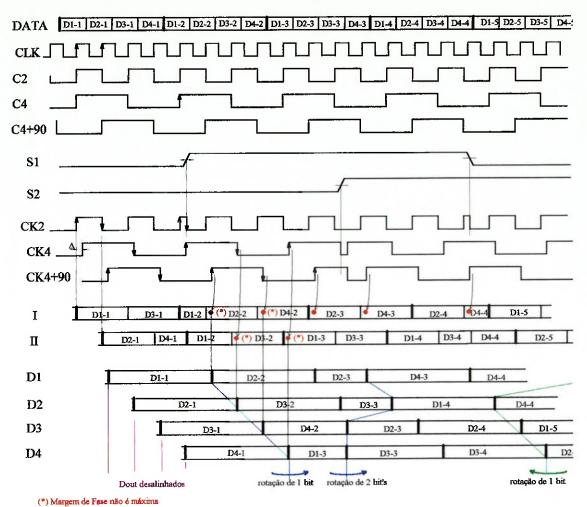

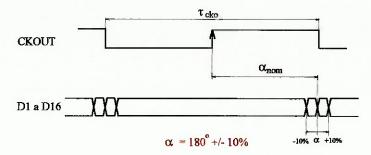

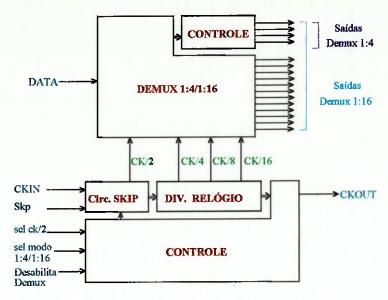

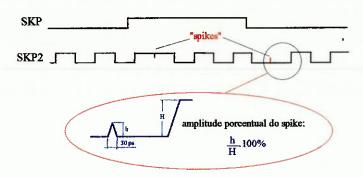

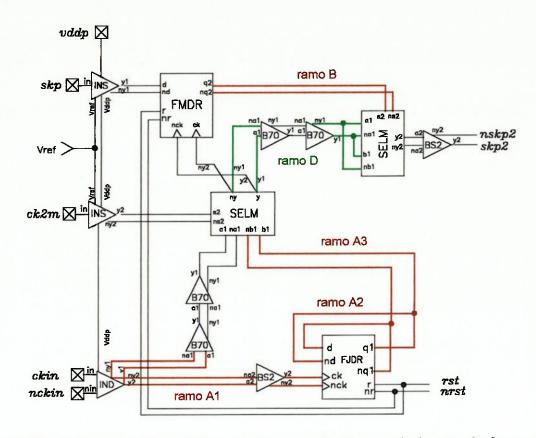

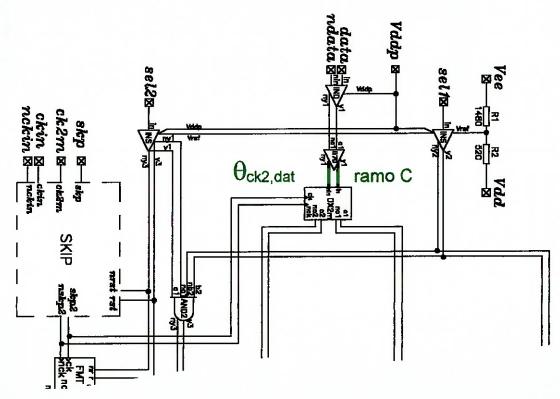

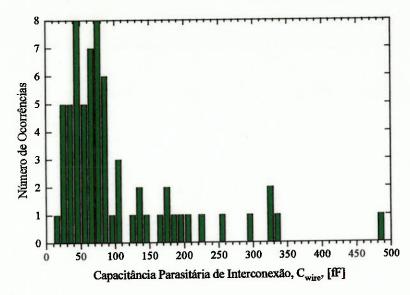

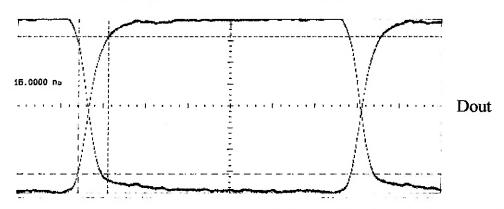

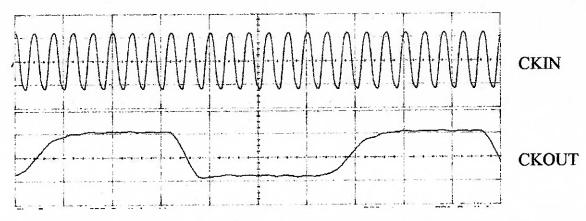

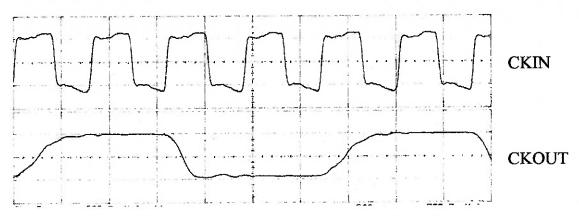

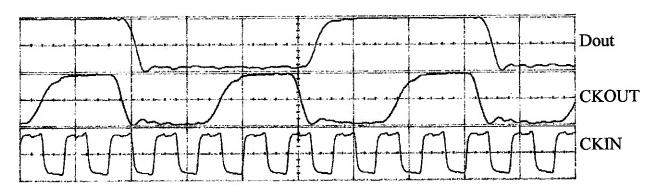

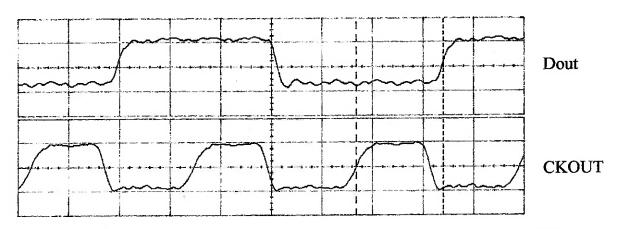

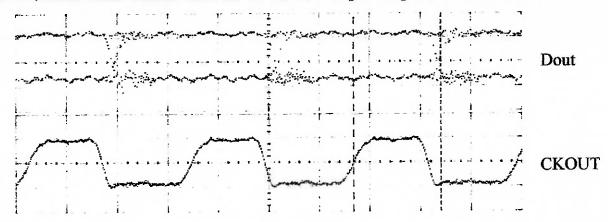

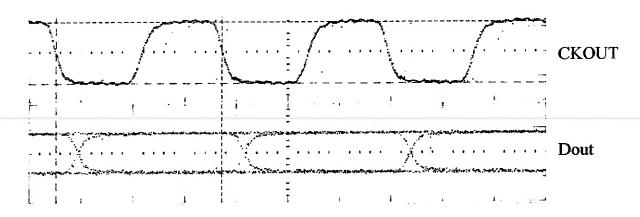

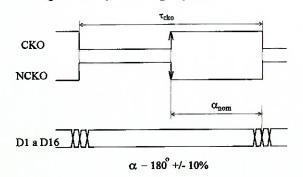

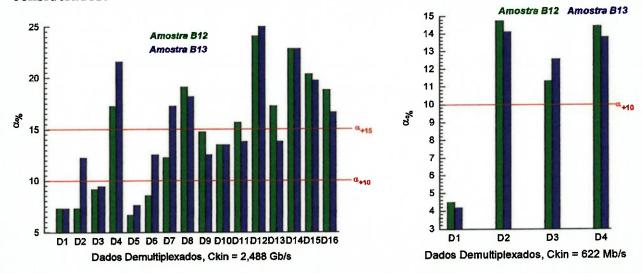

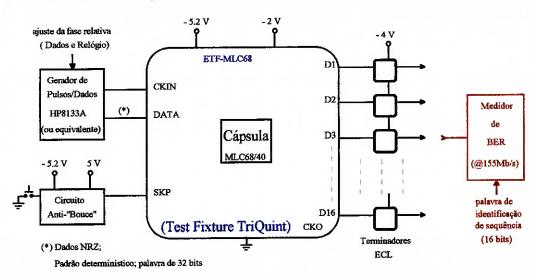

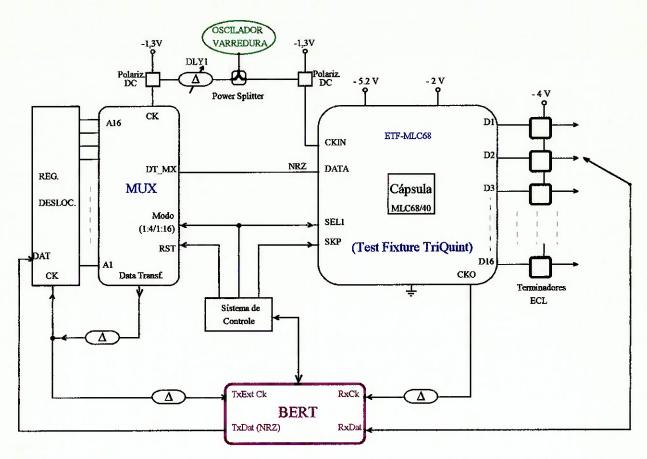

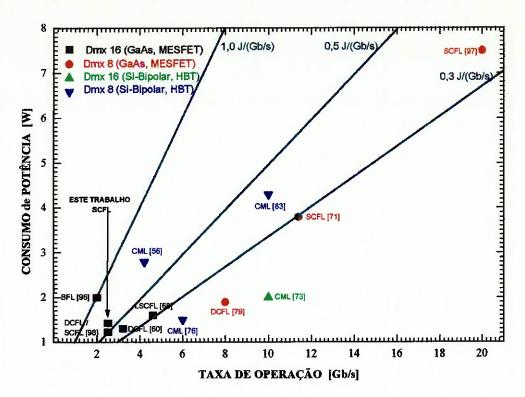

### Quasi-FET Logic (QFL)